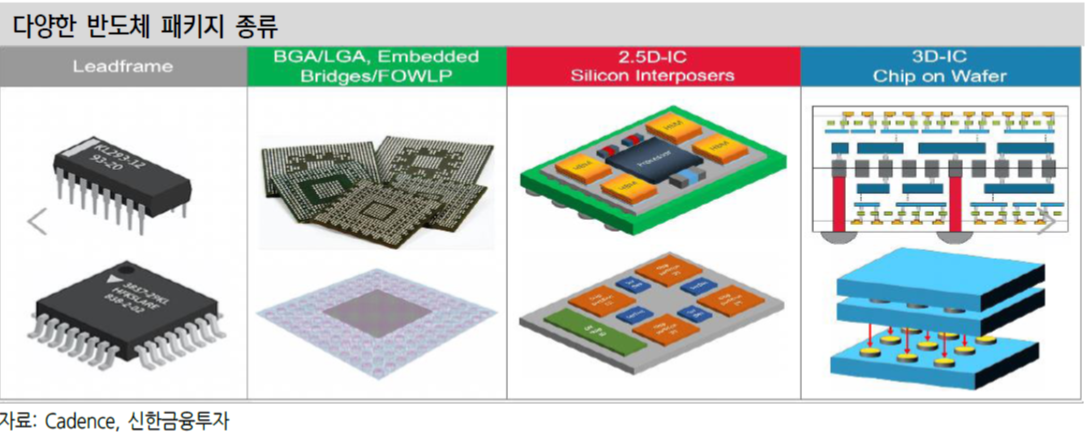

4. 반도체 패키징 소재 및 공정의 개요

4.1. 반도체 패키징의 필요성

실리콘 웨이퍼에 가공된 칩은 그 자체로 반도체로 기능할 수 없다. 반도시 패키징을 통해 칩에 있는 전기적 신호를 전자제품의 보드에 물리적으로 연결해 전기적 신호가 전달될 수 있도록 만들어줘야 한다. 반도체 패키징의 기본적인 목적은

1) IC칩과 이것이 장착되는 전자제품 보드까지의 전기적 신호의 연결,

2) 깨지지 쉬운 실리콘 IC칩 보호,

3) 장시간 다양한 환경에서 사용될 수 있도록 신뢰성의 확보이다.

4.2. 반도체 패키의 주요 소재

반도체 패키지 주요 소재는 실리콘 칩, 기판, 금속선(리드프레임), 범프(솔더볼), 몰딩 컴파운드, 접착제 등이다.

1) 기판(Substrate): 반도체 칩이 실장되고, 칩과 PCB간 전기적 신호를 연결해준다. 절연층 위에 전기적 신호를 전달할 수 있는 도체를 배열한 구조로, 칩의 미세한 배선을 메인 PCB의 스케일로 변환해준다.

2) 금속선(Metal Wire): 반도체 칩과 기판을 연결해주는 얇은 전선이다. 주로 금이나 구리로 만든 리드프레임이 사용된다.

3) 범프(Bump): 반도체 칩과 기판을 전기적으로 연결해주는 금속 돌기이다. 최근에는 반도체의 경박단소화를 위해 금속선 대신 범프가 사용되는 추세이다. 주석, 은, 구리 등으로 만들어진 솔더볼(Solder Ball)이 주요 사용되는데 사실 솔더볼이 좀더 큰 것이고, 범프는 작은 것을 의미한다.

4) 몰딩 컴파운드(Molding Compound): 제품 최종 성형 및 부품 고정을 위해 사용된다. Epoxy라는 수지가 주로 사용되어 EMC(Epoxy molding Compund)라고도 한다.

5. 반도체 패키징 공정

1) Back Grinding: 전공정에서 가공된 웨이퍼의 후면을 얇게 갈아내는 공정

2) Sawing(Dicing): 웨이퍼를 개발 소자 조각 개별 단위(net die)로 잘라내는 공정

3) Die attaching: 회로기판(Substrate)에 찹을 붙여 고정하는 공정

4) Wire bonding: Gold wire로 칩을 전기적으로 연결하는 공정

5) Solder ball mount: 회로기판에 솔더 볼을 붙여 아웃단자를 만드는 공정

6) Molding: EMC 물질로 칩이 실장된 기판을 감싸는 공정

7) Marking: 레이저로 Molding 표면 위에 개별 제품 정보를 새기는 공정

8) PKG Sawing: 모듈/보드/카드에 실장하도록 개별 반도체로 잘라내는 공정

6. 반도체 패키징 테스트 공정

1) Assembly out: 제품 종류, 수량, I/O 수 (bit) 수 등을 확인하는 공정

2) DC Test & Loading / Burn-in: 선행 공정을 거치면서 발생된 불량을 선별한 후 제품에 고온, 고전압 등의 극한 조건을 가해 신뢰성을 확인하는 공정

3) Post burn-in: 상온 및 저온에서 전기적 특성 및 기능을 검사하는 공정

4) Final test: Burn-in 테스트 이후 제품의 작동 여뷰를 검사하는 공정

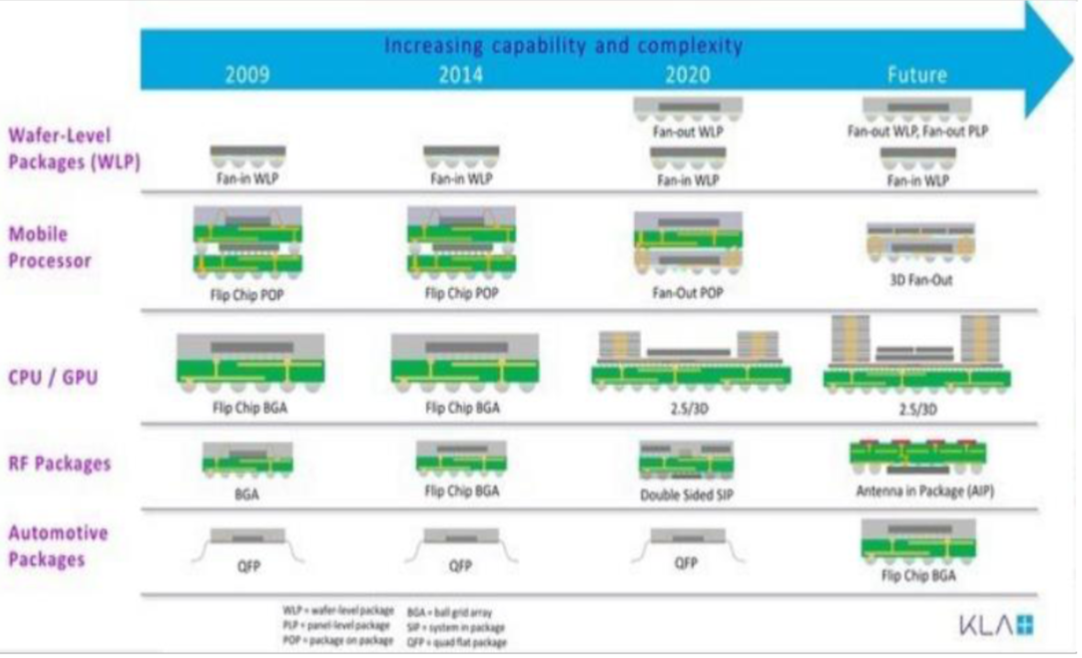

7. 반도체 패키징 기술 변화: 최소 크기와 최대 성능의 교집합

응용 분야를 막론하고 반도체 패키징을 물리적으로 얇고 크기를 작게(경박단소) 하면서 대용량을 처리할 수 있게 하는 것이 목표이다.

전기적으로는 전력 소모를 줄이면서 안정적이고 빠른 신호 배선 설계가, 열적으로는 효율적으로 열을 방출하는 것이 중요하다.

이런 물리적, 전기적, 열적 특성을 만족하면서 가격 경쟁력을 갖춘 패키징 기술이 시대마다 주요 트렌드가 되어 왔다.

8. 차세대 반도체 패키징

1) FC-BGA(Flip Chip-Ball Grid Array)

BGA는 패키지와 메인 PCB와의 연결 방식을 금속선에서 범프로 전환한 것이다. BGA의 도입으로 I/O 단자 수가 획기적으로 증가했다.

플립칩 본딩은 칩의 외부 입출력 단자인 패드 위에 범프(Bump)를 형성시킨 후에 칩을 뒤집어서 기판과 맞대어 본딩하는 방식이다.

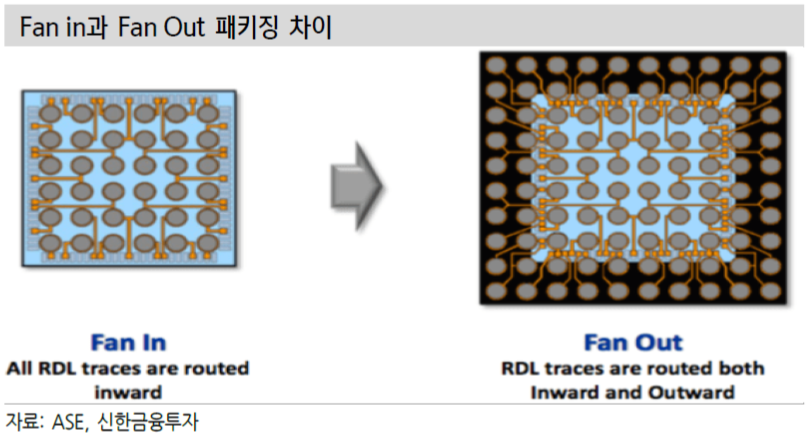

2) FO-WLP (Fan Out-Wafer Level Package)

Fan out은 칩 바깥 쪽에 패키지 I/O(Input/Output) 단자를 배치하는 방식이다. 칩 크기가 작아지더라도 표준화 볼 레이아웃을 그대로 사용할 수 있다.

DLP(Die Level Package)가 웨이퍼 상의 칩을 절단한 이후 패키징을 하는 방식이라면, WLP는 웨이퍼 상에서 패키징이 진행되는 것이다. 따라서 패키지 I/O 단자가 칩 안쪽에 배치된다. 기존 패키지 대비 소형화, 박형화에 유리하다. 열적, 전기적 특성이 우수하고 인쇄회로 기판을 사용하지 않아 원가 절감이 가능하다.

PLP(Panel Level Package)는 원형 웨이퍼 대신 사각 패널에서 공정을 진행한다. 버리는 면적이 적어지기에 WLP 보다도 수율을 높일 수 있다.

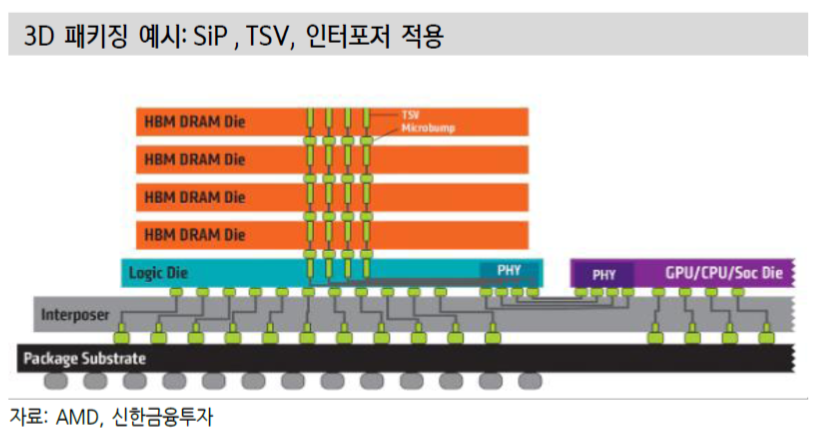

3) 3D 패키징, SiP (Sytem in Package)

작은 면적에 다수의 칩을 패키지하기 위해 3D 패키징 기술이 개발됐고, 칩과 수동소자가 함께 내장되는 모듈 형태의 패키지도 새롭게 등장하고 있다.

SiP(System in Package)은 기판 위 서로 다른 기능의 능동소자들을 올린 후 하나의 패키지로 만드는 것이다. 소자 간 거리를 최대한 단축시켜 대량 정보를 빠르게 전달하기 위한 목적이다.

인터포저(Interposer)는 실리콘 웨이퍼 위에 칩들을 얹거나 실장하고 기판에 구멍을 뚫은 후 내부를 전도체로 채워 칩 간 또는 칩과 PCB 간을 전기적으로 연결하는 것이다. 인터포저 사용시 물성이 다른(Pad의 위치와 크기가 다른) 다양한 칩을 패키징할 수 있다.

TSV(Through Silicon Via)은 두 개 이상의 칩을 수직 적층하고 실리콘 관통 전극으로 회로를 연결하는 방식이다. 실리콘 웨이퍼의 상하부를 전극으로 연결하여 최단거리 신호 전송경로를 제공해 패키지 경박 단소화에 가장 유리하다.

To-be Continued

출처: 신한금융투자, ASE, AMD, KLA, Cadence, Toppan

뜨리스땅

https://tristanchoi.tistory.com/189

반도체 기술 탐구: OSAT과 패키징 - 3

9. 삼성전자의 전략: Fan Out & TSV 9.1. Fan Out과 TSV F/O 또는 TSV는 전공정이 완성된 반도체 칩에 추가적으로 고성능, 고용량, 저전력화를 더할 수 있다. TSV가 궁극적인 기술로 예상되며, F/O은 TSV 기술이

tristanchoi.tistory.com

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체 기업 탐구: 넥스틴 (0) | 2021.03.17 |

|---|---|

| 반도체 기술 탐구: OSAT과 패키징 - 3 (0) | 2021.03.12 |

| 반도체 기술 탐구: OSAT과 패키징 - 1 (0) | 2021.03.11 |

| 반도체 기업 탐구: 한미반도체 (0) | 2021.03.10 |

| 반도체 기업 탐구: 테스(TES) (0) | 2021.03.10 |

댓글