일전에 다른 포스팅에서도 후공정에 주목해야 하는 이유를 몇번 설명했지만, 최근 상황들을 고려해서 다시 한 번 정리해 보려한다.

과거와 같이 전공정 기술 개발에만 집중하는 시기는 끝났다. 과거에 주목받지 못 하던 후공정이 아니다. 생산업체는 특히 반도체 고성능화 및 원가절감에 기여할 수 있는 후공정 기술 확보에 노력 중이다. 반도체 요구량은 계속 증가하고 사용 할 수 있는 재원은 한정돼있다. 생산업체는 상대적으로 부가가치가 낮은 제품에 대한 OSAT 외주 물량 확대를 지속할 수 밖에 없는 이유다. 결국 첨단패키징 기술 개발에 따른 반도체 생태계 변화는 OSAT 업체의 수혜로 현재 진행 중이다.

4차 산업혁명에 따른 전방 수요 확장

1970년대 회로 선폭은 100um(1um = 1,000nm)에서 현재 3nm까지 1/100,000 수준의 엄청난 정도로 미세화가 진행됐다. 하지만 4차 산업혁명을 중심으로 반도체 고성능화 요구는 여전히 계속되고 있다. 50년 넘게 전공정 기술이 개발되며 개발 난이도는 급격하게 상승했다. 이에 따른 수율 악화 및 개발 비용 증가로 새로운 시도들이 계속되고 있다. 후공정 기술은 엄청 새로운 기술은 아니다. 단지 전공정 기술 개발 한계에 따라 기술 개발 중점이 전공정에서 ‘전공정+후공정’으로 변한 것이다.

반도체 고성능화 요구 지속

4차 산업혁명으로 클라우드, 빅데이터, AI 기술 등 더 빠르고 많은 데이터 처리에 대한 요구가 높아지고 있다. 이는 AI반도체를 포함한 고성능 반도체 수요 확장으로 연결된다. 반도체 동작 속도(초당 데이터 전송 수)를 높이고 I/O(전기신호 연 결 통로)를 확장하기 위한 개발이 반도체 전공정 및 후공정 전방위적으로 이뤄지고 있는 이유다. 반도체 기술 개발은 더 이상 전공정에만 국한되지 않는다.

2. 한계가 다가오는 전공정 기술 개발

50년 넘게 지속된 공정 미세화 노력

반도체 후공정이 주목을 받는 이유는 간단하다. 전공정 기술 개발을 통한 반도체 성능 향상에 어려움을 겪고 있기 때문이다. 역사적으로 반도체칩의 성능 개선은 공정 미세화를 통해 이뤄졌다. 선폭이 작아질수록 반도체 칩 안에 더 많은 트랜지스터를 넣을 수 있고 전자의 이동거리를 단축시킬 수 있다. 이는 반도체 소자의 동작 속도를 향상시키기 때문이다.

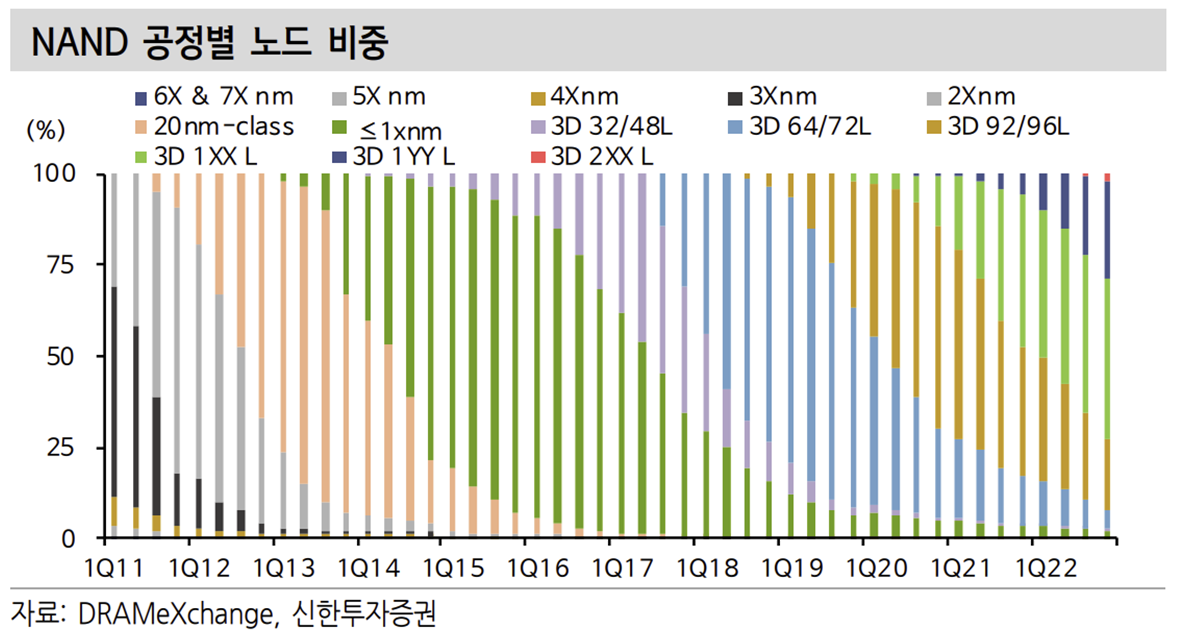

반도체의 선폭은 2022년 3nm까지 줄어드며 상당 수준 미세화됐다. 2000년 (180nm) 대비 60분의 1 수준이다. 로직 반도체 뿐만 아니라 메모리 반도체 또한 멀티 패터닝과 3D 적층 기술 등을 접목해 집적도를 높여왔다. 현재 디램은 13- 14nm, 낸드는 238단 수준까지 개발됐다. 하지만 공정 기술 개발 난이도가 높아짐에 따라 반도체 성능 고도화 과정은 순탄하지만은 않았다.

단채널현상(Short Channle Effect)은 트랜지스터 내 채널 길이가 짧아지며 전류 조절 기능을 상실하는 현상을 말한다. 누설전류(Leakage Current)가 가장 대표적인 문제로 트랜지스터의 동작 속도를 저하시키고 전력 소모를 증가시킨다. 원자 하나 크기가 옹스트롬(1/10,000,000,000) 단위인데, 현재의 미세 공정 수준인 3nm는 원자 몇 십개 정도를 연결한 길이이기 때문이다. 개인적으로는 반도체 공정의 미세화가 10nm로는 물리적으로 불가능 할 것으로 생각했었다.

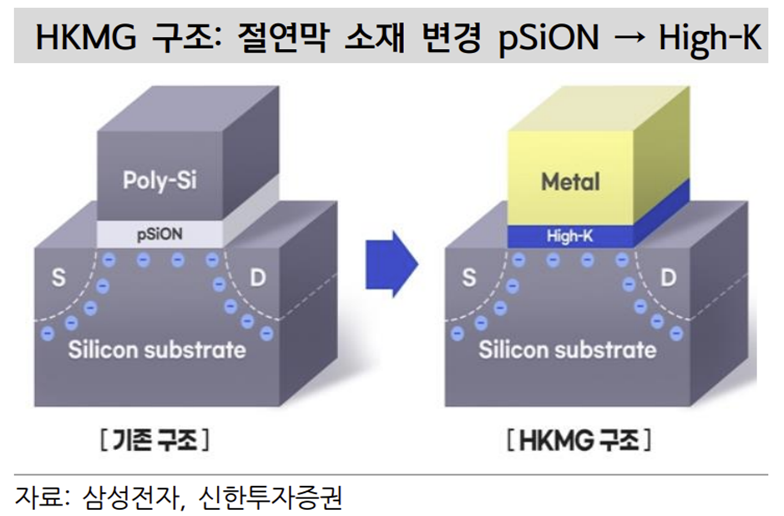

하지만, 반도체 업체들은 새로운 공정 기술(HKMG, FinFET, GAA)을 통해 이를 해결하기 시작했다.

HKMG(High-K Metal Gate)는 트랜지스터 내에 절연막 소재를 유전율이 높은 물질로 대체하여 전기 저항을 높인다. 이는 회로 간 누설전류가 흐르는 것을 막아준다. 인텔은 2007년 처음으로 HKMG 공정을 적용한 반도체를 생산했다.

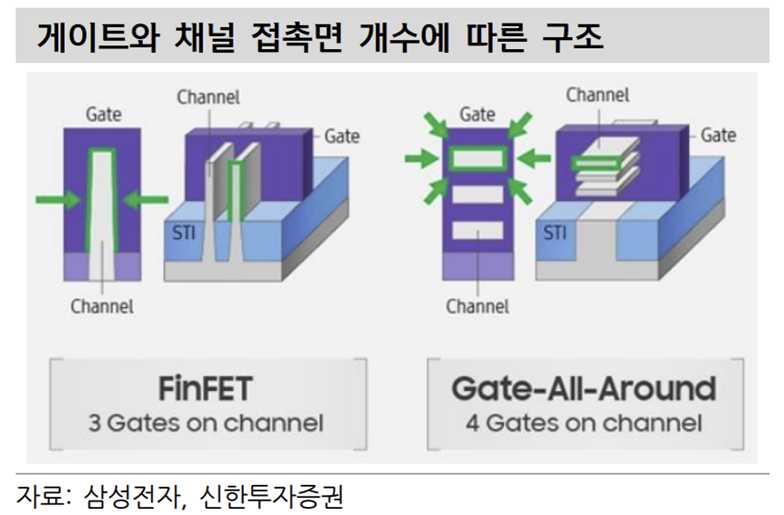

또한 트랜지스터 구조를 바꿔 전류가 잘 컨트롤하는 방법도 개발됐다. 2011년 게이트와 채널의 맞닿는 면이 2개(Planar)에서 3개(FinFET)로 증가했고, 2022년 4 개의 면이 맞닿는 GAA(Gate-All-Around)기술이 처음으로 적용됐다. GAA 기술은 전류의 흐름을 제어하는 게이트와 채널의 접촉면이 많아져 전류 흐름을 세밀하게 제어한다. 이를 통해 전력 효율성을 높일 수 있는 구조다. 결국 공정 미세화뿐만 아니라, 이에 수반되는 단채널현상을 해결하기 위한 노력이 함께 요구 된다. 전공정 기술 개발이 어려운 이유다.

공정 미세화에 따른 요구 CapEx 증가

공정 미세화에 기술 개발 수준이 어려워지며 반도체 개발에 대한 투자비용이 급격하게 증가하고 있다. 우선 반도체 칩 설계 부문의 개발 난이도가 급격하게 상승했다. 5nm 설계 비용이 5억 달러(약 6,400억원) 수준까지 증가한 것을 보면 알 수 있다. 이는 28nm 대비 약 11배 증가한 금액이다.

반도체 제조 공정도 마찬가지다. 공정 미세화를 위해 패터닝 횟수가 증가하고 더 미세한 파티클(오염줄일)을 검출하기 위한 MI공정이 증가하고 있다. 공정스텝이 1,000개(5nm 기준)를 넘어가며 공정 비용이 크게 증가했다. EUV 장비를 도입해 공정스텝을 줄일 수 있지만 장비 가격이 많이 비싸다. ASML의 EUV 노광장비는 현재 약 2,000억원이며 차세대 장비는 5,000억원 수준으로 예상된다.

결국 반도체 증설에 따른 요구 CapEx 증가는 불가피하다. 실제로 파운드리 Capa 100K 당 요구 CapEx를 보면 28nm 120억 달러에서 5nm 320억 달러로 크게 증가했다. 전공정 기술 개발을 통한 원가 절감 폭이 감소하며, 반도체 패키지 기술을 통한 성능 고도화 및 원가 절감이 주목받고 있다.

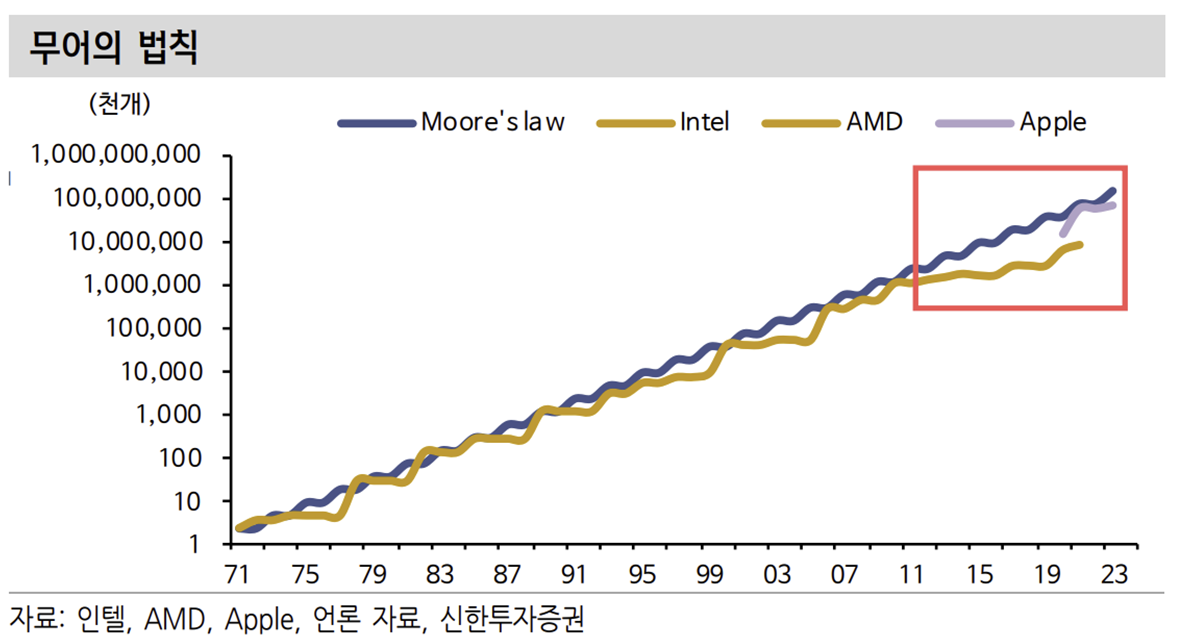

무어의 법칙 사실상 폐기

1975년부터 반도체 성능 향상의 척도였던 무어의 법칙은 2014년부터 흔들리기 시작했다. 인텔은 2014년 처음 14nm 기반의 CPU를 출시한 이후, 7년이 지난 2021년이 되서야 10nm 기반의 CPU를 생산할 수 있었다. 2년에 한번 이뤄져야 할 공정 미세화가 무려 6-7년이 걸렸다.

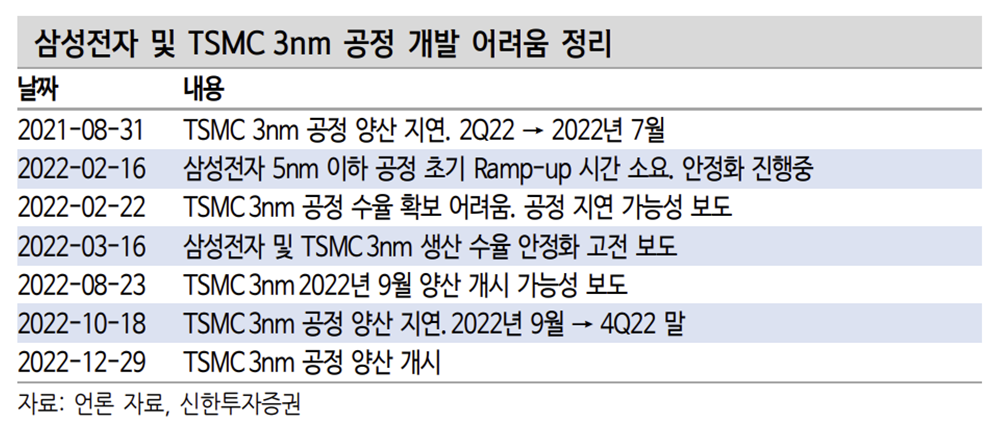

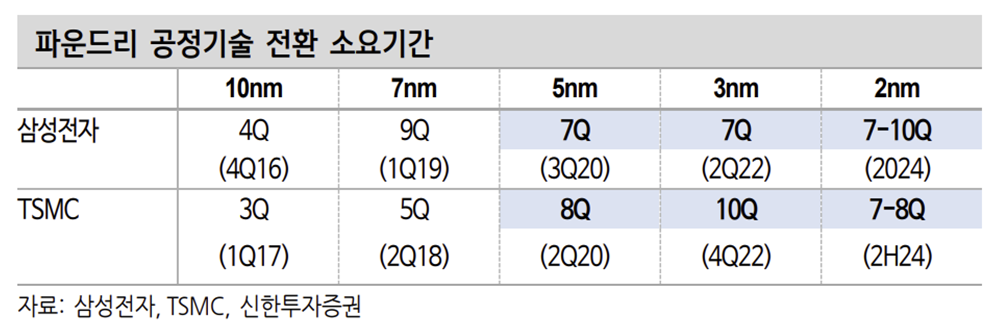

또한 2016년 무어의 법칙 달성에 기반이되는 틱톡(Tick-Tock)전략을 포기하며, 공정 개발 주기를 2년에서 3년으로 늘 렸다. 공정 미세화에 따른 높은 기술 개발 난이도 때문이다. 삼성전자와 TSMC 또한 이런 어려움을 피해갈 수는 없었다. 수율 안정화에 부정적인 영향을 받기도 하고, 공정 개발 양산 지연을 발표하기도 했다.

to be continued...

출처: 삼성전자, TSMC, 신한투자증권, Apple, Intel

뜨리스땅

https://tristanchoi.tistory.com/419

반도체 산업 탐구: OSAT 기업들의 실적 변수 모음

OSAT 반도체 생태계 안착 기술 개발 요구: 전공정 → ‘전공정 + 후공정’ 지난 50년 넘게 반도체 기술은 전공정 기술에 집중했다. 하지만 4차 산업혁명으 로 고성능 반도체가 요구되고, 전공정 기

tristanchoi.tistory.com

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체 산업 탐구: 한국 반도체 생태계에서 OSAT 위치는? (2) | 2023.04.16 |

|---|---|

| 반도체 산업 탐구: 한국 OSAT 업체의 실적에 영향을 주는 변수는? (1) | 2023.04.16 |

| 반도체 산업 탐구: OSAT 기업들의 실적 변수 모음 (1) | 2023.04.12 |

| 반도체 산업 탐구: 미래의 일 - AI와 일하기 (0) | 2023.03.27 |

| 반도체 산업 탐구: 비 메모리의 미래 - 인공지능 AI (2) | 2023.03.26 |

댓글