DRAM, NAND, 비메모리 반도체 모두 트랜지스터라는 구조를 모두 포함하고 있다. 이러한 구조를 기반으로 구성되어 있기 때문에 반도체 소자의 성능은 트랜지스터와 직결된다.

트랜지스터는 입력과 출력 사이에 시간 차가 발생하며 이를 게이트 딜레이라고 부른다. 게이트 딜레이는 회로의 속도가 낮아지는 주요 원인이며 전류의 양과 반비례한다. 이에 따라 트랜지스터의 발전은 전류의 양을 늘리는 것이 주축이 되어 왔다.

포화 전류(Saturation current) 방정식을 보면 전류의 양은 게이트의 폭(W), 전하 운반체의 이동성(μ), 유전막의 capacitance(C)에 비례하며 채널 길이(L)에 반비례한다. 또한 유전막의 capacitance 는 유전막의 유전율(ε), 면적(A)과 비례하며 유전막의 두께(t)와 반비례한다.

결국 전류의 양을 늘리기 위해선 1) 채널 길이 단축 및 게이트 폭 증가 2) 전하 운반체 이동성 향상 3) 유전막의 capacitance 개선이 필요한 셈이다.

1) 전하 운반체 이동성 향상 --> epitaxy 수요 촉진

포화 전류 방정식에서 전하 운반체 이동성(μ)을 향상시키기 위한 방법으로는 실리콘에 기계적인 stress 를 주는 Biaxial strain(2 축 변형)과 Uniaxial strain(1 축 변형) 방법이 있으며 두 방법 모두 epitaxy(단결정 성장법)가 사용된다.

2002 년에 인텔이 최초로 Uniaxial strain 을 통해 90nm 급 반도체 양산에 성공하였으며 epitaxy 로 strain 층을 형성시켜야 하기 때문에 uniaxial strain 의 도입은 epitaxy 기술의 수요를 촉진시켰다.

Epitaxy 는 기판이 되는 단결정 Seed-layer 위에 단결정 물질을 성장하는 기술이다. Seed-layer 와 에피택셜 층의 결정 구조 간격이 일치하면 호모 에피택시(Homo Epitaxy, 격자정합)라고 하며, 일치하지 않으면 헤테로 에피택시(Hetero Epitaxy, 격자부정합)라고 부른다.

헤테로 에피택시에서 에피층의 결정격자 간격이 Seedlayer 보다 크면 압축 응력이 가해지고, 반대의 경우 인장력이 가해지는 원리를 활용해 전하 운반체의 이동성을 향상시킬 수 있다. Biaxial strain 은 웨이퍼 전면으로 stress 를 가해주는 방법이다.

Biaxial strain 방식을 적용하면 양산하기 어려울뿐더러 stress 가 수직 방향으로도 가해지면서 이동성 향상 효과가 떨어지기 때문에 현재 반도체 소자 업체들은 Uniaxial strain 을 주로 사용하고 있다.

Uniaxial strain 은 채널에서 전류가 흐르는 방향으로만 stress 를 주는 방법이다. Uniaxial strain 은 크게 채널에 압력을 주는 compressive strain 과 바깥으로 끌어당기는 tensile strain 으로 나뉜다.

PMOS 의 경우 drain 과 source 의 Si 를 제거한 후 SiGe 를 epitaxy 로 성장시켜 채널에 응력을 가하는 방법이 사용되며, NMOS 는 Si3N4 레이어를 트랜지스터 상층에 씌워 채널에 인장력을 가하는 방법을 사용한다.

2) 유전막의 capacitance 향상 --> High-k 소재, ALD 증착 수요 촉진

유전막은 게이트 아래 위치한 얇은 절연막으로 게이트에 전압이 가해지면 채널에 있는 전하를 유전막 아래로 모아주는 역할을 한다. 유전막 아래에 더 많은 전하가 모일수록 전류의 양이 많아지기 때문에 유전막의 capacitance 와 전류는 정비례 관계를 갖는다.

또한 유전막의 capacitance 는 유전막의 유전율(ε), 면적(A)과 정비례하며 유전막의 두께(K)와 반비례하기 때문에 결과적으로 전류 양을 늘리려면 높은 유전율을 가진 유전막 채택, 유전막의 면적 확대, 두께를 감소하는 방법이 있다.

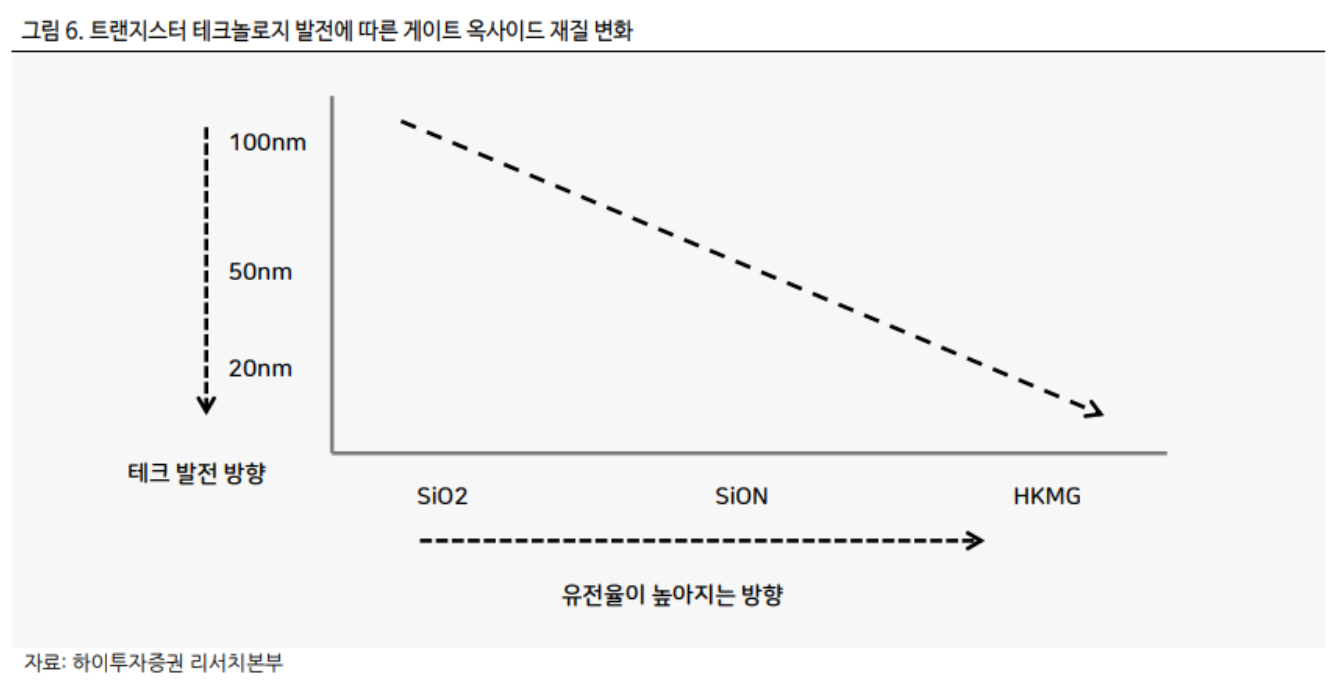

트랜지스터의 집적도가 향상될수록 유전막의 면적도 줄어들기 때문에 면적을 늘리는 방법으로 유전막의 capacitance 를 높이는 방법은 제한적이다. 이에 따라 유전막 두께를 줄이는 방법이 사용됐는데 게이트의 폭이 10nm 대가 되고 유전막 두께가 1nm 대로 감소하게 되면서 터널링 현상이 나타났다.

터널링 현상이란 전자나 원자핵 같은 입자들이 역장의 장벽을 투과하는 현상을 일컫는다. 트랜지스터의 경우 유전막이 얇아질 경우 실리콘 층에 있던 전하들이 얇아진 유전막을 뚫고 나가 누설 전류가 발생하고 이는 트랜지스터 성능을 저하시키는 요인이 된다.

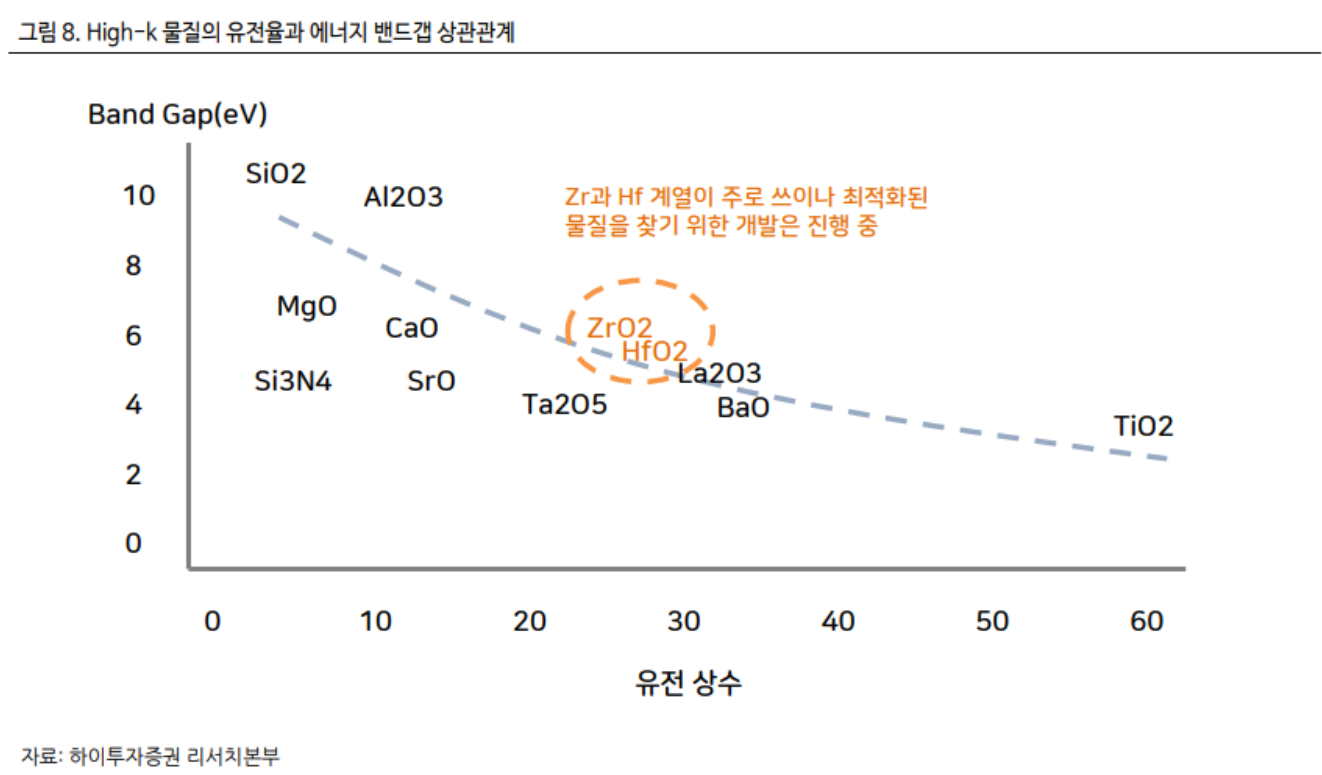

유전막의 면적과 두께를 조절하는 방법이 한계에 이르자 반도체 소자 업체들은 높은 유전율을 지닌 유전막을 사용하게 되었으며 그게 바로 흔히 알려진 High-k(고유전율) 유전막이다.

High-k 유전막 소재로는 HfO2, ZrO2, Al2O3, HfAlO 등이 있다. 기존 유전막으로 사용되던 SiO2 의 유전 상수는 3.9 이며 이보다 크면 High-k, 작으면 Low-k 라고 불린다. 유전 상수가 24 가 넘는 Hf(하프늄) 기반 유전막을 쓰면 SiO2 같은 성능이여도 유전막의 두께를 1/6 로 줄일수 있는 셈이다. 현재 High-K 전구체를 생산하는 국내 업체로는 솔브레인, 한솔케미칼, SK 머티리얼즈, 오션브릿지, 메카로, 디엔에프가 있다.

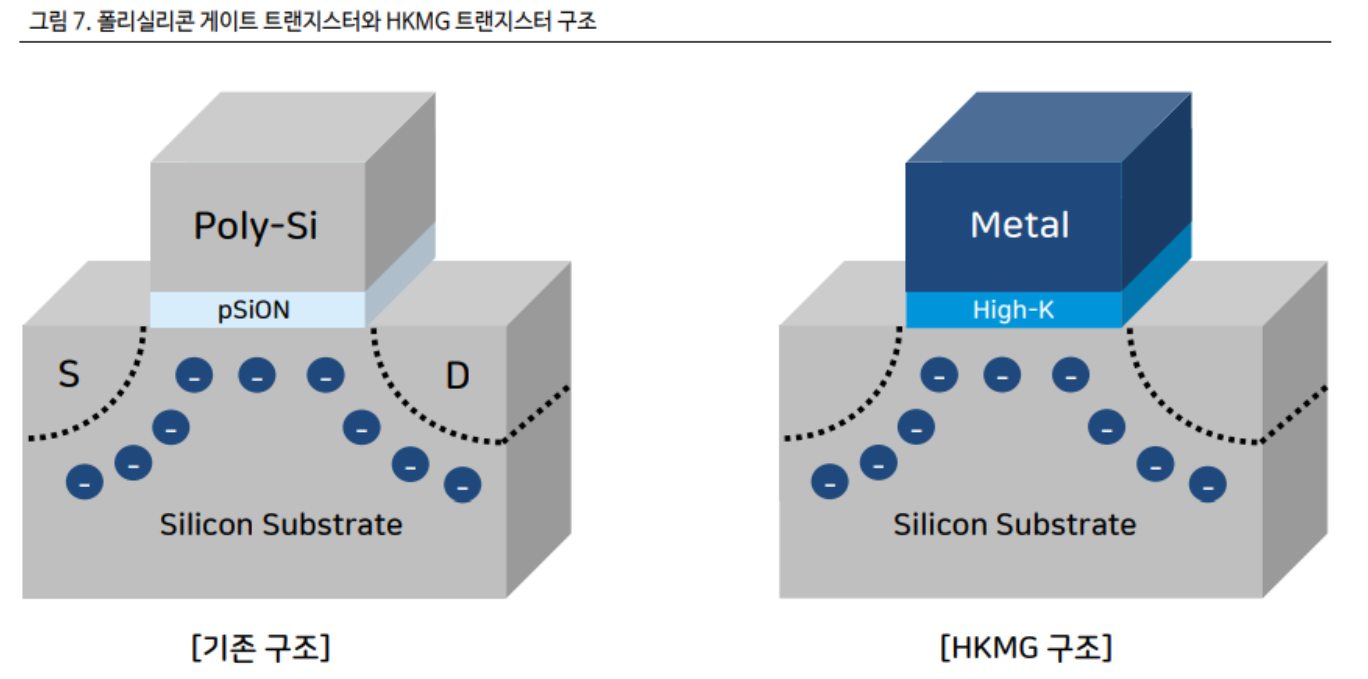

100nm 반도체까지는 주로 메탈 게이트가 사용됐으나 반복되는 열처리에 녹는 문제점이 발생하자 도핑된 폴리실리콘이 사용되기 시작했다. 폴리실리콘의 경우 실리콘 기판과 접촉 특성도 뛰어났고, 융점도 1,400 도 이상이기 때문에 게이트로 쓰이기에 적합하다는 평가를 받았다.

이에 따라 폴리실리콘 게이트도 High-k 절연막과 사용하려는 시도가 있었으나 반복되는 열처리로 인해 High-k 절연막과 폴리실리콘이 반응해 SiO2 층을 생성한다는 문제가 발생했다. SiO2 산화막이 형성되면 유전막의 유전율이 감소해 capacitance 도 낮아지며 전기 이동도를 저하시키는 문제가 발생한다. 결국 High-k 절연막을 사용하기 위해 다시 메탈 게이트를 사용하고 있으며, 이러한 구조를 HKMG(High-K Metal Gate)라고 부른다.

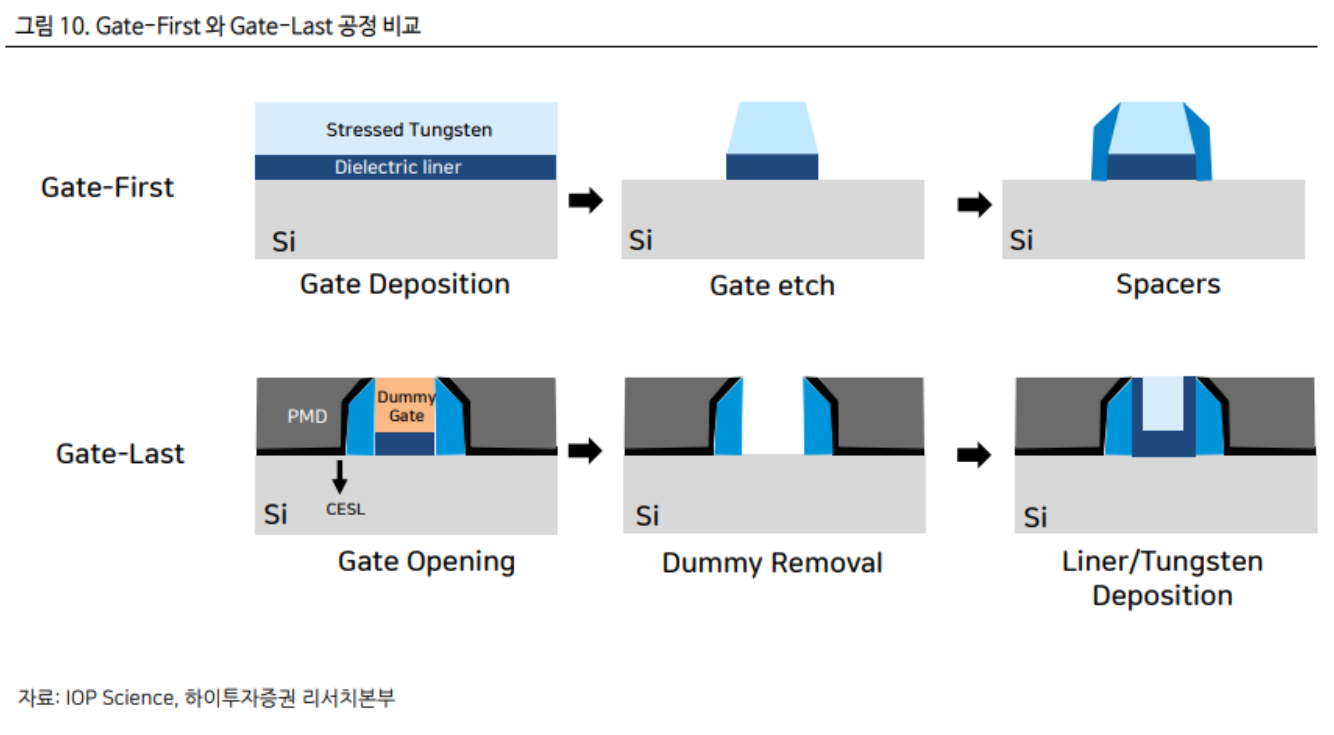

반도체 소자 업체들은 HKMG 에서 메탈 게이트의 낮은 융점을 해결하기 위해서 더미게이트를 생성하는 방법을 고안해냈다. 메탈게이트의 자리에 폴리실리콘으로 형성된 더미게이트를 채워 넣고 열처리 공정이 끝난 후 더미게이트를 식각하여 메탈게이트를 채워 넣는 방식이다. 이러한 방법을 RMG(Replacement Metal Gate) 또는 Gate Last 라고 부른다. RMG 는 증착, 식각, CMP, 세정 공정이 더 추가되기 때문에 공정 Step 수 증가에 기인한다.

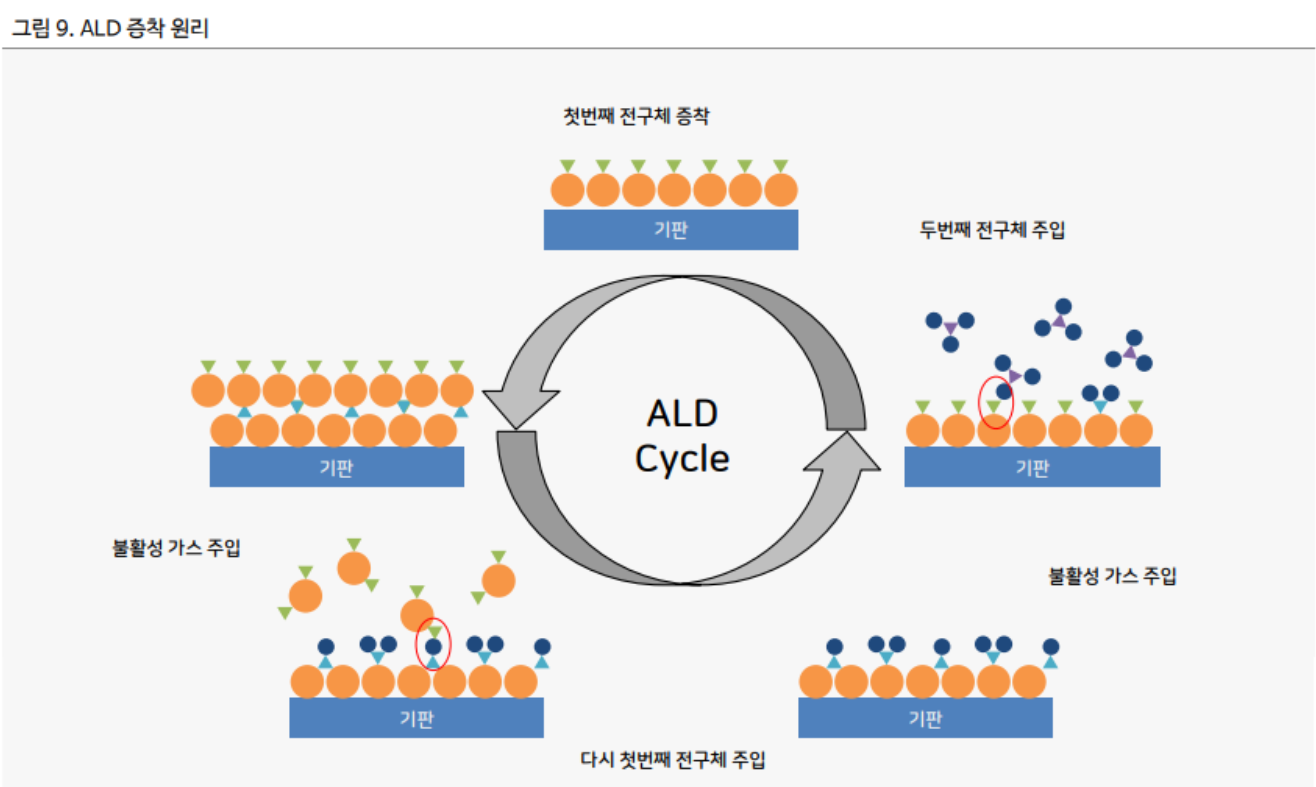

반도체 소자 업체들이 High-k 유전막을 도입하면서 원자 단위의 두께로 증착 가능한 ALD(Atomic Layer Deposition)에 대한 수요도 증가했다. 기존 SiO2 유전막의 경우 실리콘을 산화시키면 됐지만 High-k 절연막의 경우 두께를 최소화하기 위해 ALD 로 증착해야 했기 때문이다. 2021 년 기준 ALD 장비 시장 규모는 약 27 억달러 수준에 달하며 ALD 장비를 생산할 수 있는 국내 업체는 원익 IPS, 주성엔지니어링, 유진테크 등이 있다.

3) 채널 길이 단축 및 게이트 폭 증가 --> MOSFET 구조 변화 촉진

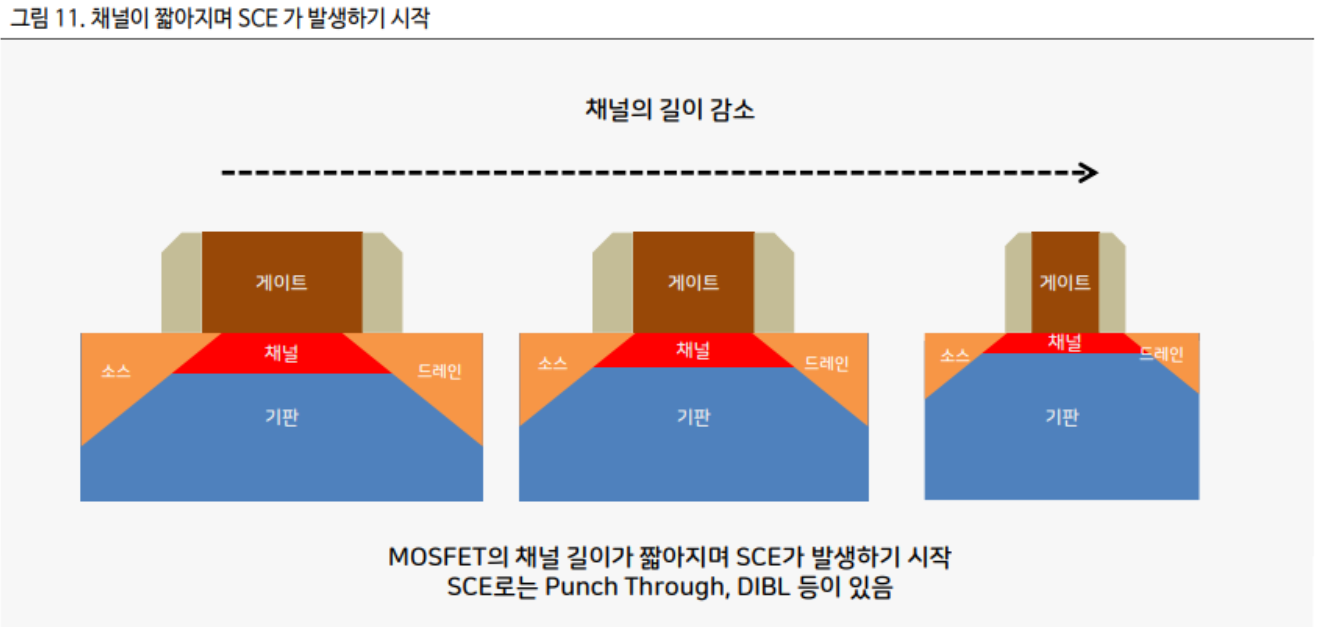

트랜지스터 Drain 과 Source 사이에 전하가 움직이는 영역을 채널이라고 한다. 채널이 짧으면 짧을수록 전하가 이동할 거리도 짧아지기 때문에 트랜지스터의 성능이 향상되는 효과가 나타난다. 다만 채널의 길이가 과도하게 짧아지면서 SCE(Short Channel Effect) 현상이 발생하기 시작했다. SCE 의 대표적인 예로는 Punch Through 와 DIBL(Drain Induced Barrier Lowering) 등이 있다.

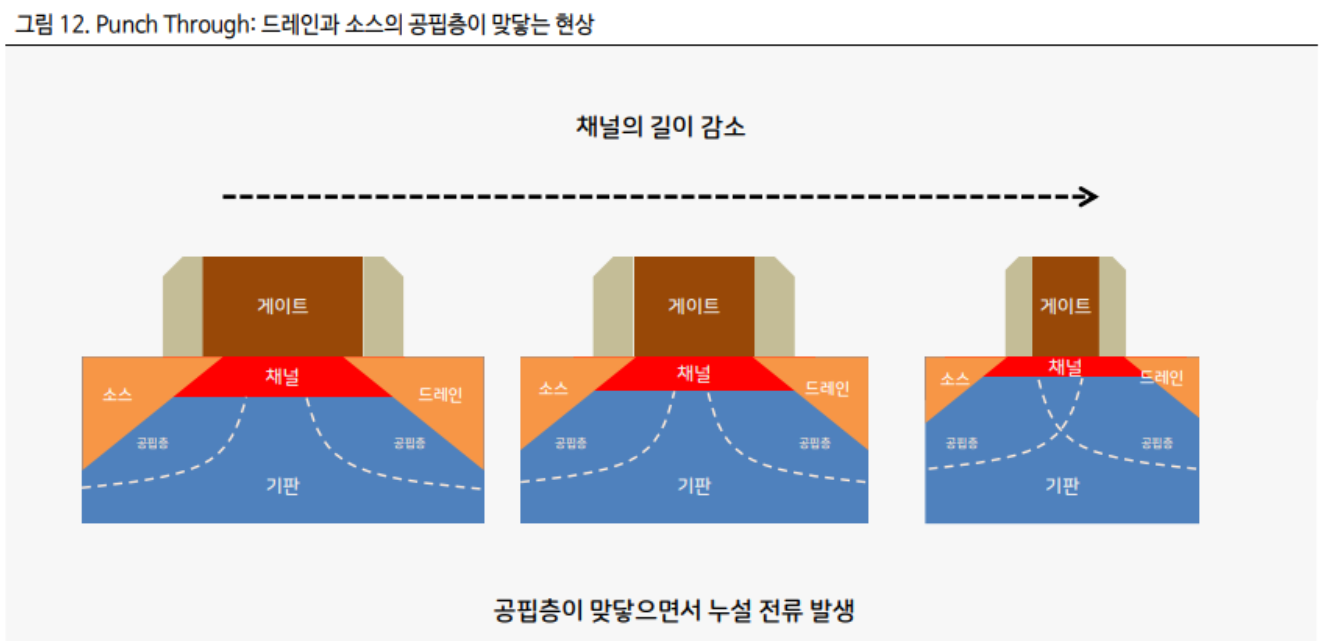

Punch Through 는 drain 과 source 사이의 거리가 좁아지면서 양측의 공핍층이 맞닿는 현상을 말한다. 공핍층이란 p 형 반도체와 n 형 반도체를 접합시키면 다수의 정공과 전자가 상쇄되어 없어지는 층이다. 공핍층에서 정공과 전자는 상쇄되어 없어지지만 공간 전하는 여전히 존재하기 때문에 drain 과 source 의 공핍층이 접촉하면 게이트의 통제와 상관 없이 전류가 흐르는 문제가 발생한다.

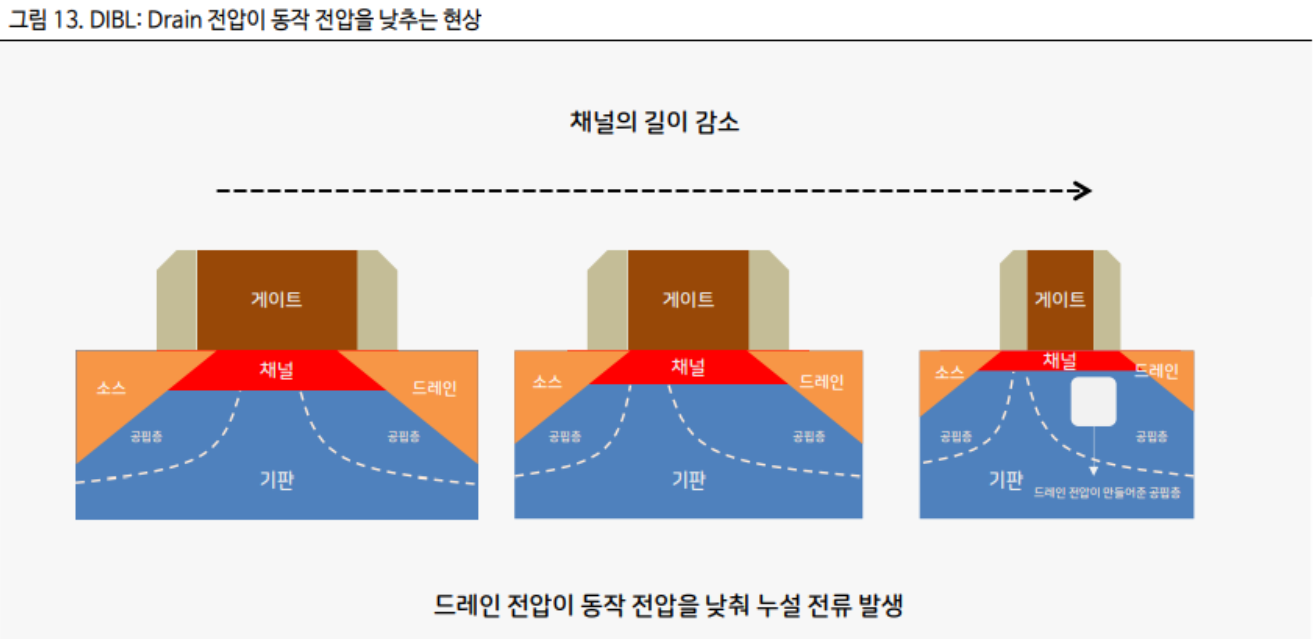

DIBL 이란 채널이 짧아짐으로 인해 drain 전압이 동작 전압을 낮추는 현상을 의미한다. Drain 전압이 공핍층을 형성함으로써 채널의 전위 장벽에 영향을 미치게 되며, 이에 따라 전위 장벽이 낮아지면서 문턱 전압이 낮아지는 현상이다. 문턱 전압이 낮아지면 게이트 구동력이 저하되며 source 에서 채널로 임의로 전하가 주입되어 누설 전류가 발생할 가능성이 크다.

MOSFET(Metal Oxide Semiconductor Field Effect Transitor)의 2 차원 구조 스케일링이 한계에 다다르면서 반도체 소자 업체들은 3 차원 구조 개발을 통해 채널 길이를 단축, 게이트 폭을 증가시켰다. 기존 Planar(평면) 구조에서 FinFET 구조를 채용하였으며 2022 년 삼성전자 파운드리 사업부를 시작으로 GAAFET 구조를 채용이 시작되고 있다.

출처: 하이투자증권

뜨리스땅

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체 기술 변화 짚어보기 - 3) NAND, 200 단을 넘는 양산 제품 (0) | 2024.09.16 |

|---|---|

| 반도체 기술 변화 짚어보기 - 2) GAAFET 채용의 본격화 (1) | 2024.09.15 |

| 삼성전자의 HBM 관련 현재 상황 및 이슈 정리 (3) | 2024.09.13 |

| NVIDIA의 Blackwell 설계 결함 및 마스크 수정 이슈 (6) | 2024.09.12 |

| CoWoS 공정에 대해 관심을 가져야 하는 이유는 무엇인가? (1) | 2024.09.11 |

댓글