1. 한국 시스템 반도체 산업 현주소

한국의 반도체 생태계는 메모리 반도체 위주이다. 반도체산업협회에 따르면 2021년 한국 반도체 총생산은 약 201조원으로 전세계 반도체 생산액의 20%를 차지한다. 하지만 같은 해 한국 시스템 반도체 세계 점유율은 3% 수준이다. 통상 시스템 반도체 시장은 메모리 반도체 대비 1.5배 더 큰 편이다. 사실상 한국 반도체 생산 대부분이 메모리 산업으로부터 나온 것이다.

AI, IoT, 자율주행 등 수요다변화로 글로벌 시스템 반도체 시장은 메모리 반도체 시장 보다 급격한 성장을 전망한다. 옴디아에 따르면 시스템 반도체 시장은 메모 리 시장 대비 2025년까지 5%p 더 높게 성장한다. 두 반도체 시장의 규모차이는 현재 1.5배에서 2025년 약 2배까지 확대될 예정이다.

삼성전자는 2023년 7월 파운드리 포럼을 통해 IP, EDA, 디자인 하우스 등 파트 너사 협력으로 파운드리 생태계를 양성하겠다고 언급했다. AI, GPU, HPC, Automotive 등 시스템 반도체 수요 증가에 대한 대응책이다. 공정이 미세화되면 새로운 IP와 EDA가 개발되기에 생태계 성장이 필연적이다.

2. 시스템 반도체, 설계부터 패키징까지

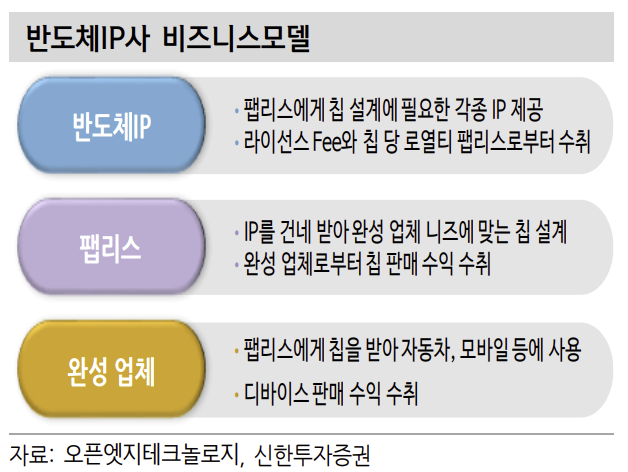

시스템 반도체의 설계부터 판매까지 전체 과정은 5개 유형의 업체들이 관여한다. 반도체IP 업체, 팹리스, 디자인 하우스, 파운드리, OSAT이다. 우선 ARM, Synopsys 같은 반도체IP 업체는 직접회로(IC, Integrated Circuit)의 주요 기능블록을 설계한다. 이 IP자산을 팹리스가 가져와 IC 설계에 활용한다.

팹리스가 인하우스 방식으로 모든 회로 블록을 설계하지 않는 이유는 중복 설계로 인한 비경제성 때문이다. 팹리스가 직접 모든 회로를 설계할 시 시간, 비용, 기능 측면에서 비효율이 발생한다. 칩 개발과 IP 산업 성장이 동행하는 이유다.

팹리스가 설계한 칩은 파운드리 업체로 넘어가 제조된다. 혹은 디자인 하우스라는 조율자를 거쳐 파운드리로 넘어간다. 팹리스는 회로 설계 전문업체도 있고, 설계 경험이 없는 기업도 있다. 따라서 파운드리가 바로 제조할 수 있도록 칩을 Backend단에서 조율해주는 디자인 하우스가 필요하다.

파운드리로 넘어온 칩은 웨이퍼 제조, 산화, 포토 등 제조 전공정과 테스트, 패키징 등 후공정을 거쳐 완성된다. 팹리스는 완성된 칩을 받아 최종으로 시스템 반도체 수요 업체에게 판매한다. 칩이 판매되면 IP자산에 대한 로열티가 인식된다.

3. 반도체IP 의미와 개발 과정

반도체IP는 집적 회로 내 재사용가능한 회로 집합을 뜻한다. 직접 회로 내 특정 회로가 IP로 판매되는 이유는 다른 칩에서도 반복되기 때문이다. 팹리스가 칩을 개발할 때 같은 기능이 반복된다면 기존에 개발한 회로를 가져다 쓰는 것이 시간과 비용 측면에서 경제적이다.

반도체IP의 개발 과정을 이해하기 위해 반도체 칩 설계와 제조 과정을 파악해야 한다. 칩 설계는 가장 기본적 기능을 C모델로 기술하며 시작한다. 이후 회로설계 레벨인 RTL(Register Transfer Level)에서 VHDL, Verilog 등 HDL(Hardware Description Language) 언어를 활용해 하드웨어 기능을 기술한다. 이 단계에서 각 동작에 필요한 비트 및 클록 회전수를 설정한다.

이후 여러 RTL 단계에서 작성한 HDL 코드를 합성(Synthesis)해 논리 회로 (Logic gate) 수준, 즉 Gate-level의 Netlist를 작성한다. 여기서 Gate는 AND, OR, NOR 등 논리값을 가진다. 여기까지 반도체 설계 전공정에 해당하며 물리적 구현을 초점으로 하는 후공정과 비교해 논리적 설계라고 한다.

물리적 설계 공정인 후공정 단계에서는 셀의 배치(Place)와 연결(Route)이 이뤄 진다. 웨이퍼 위에 올라갈 트랜지스터의 레이아웃을 그려보는 과정이다. 실제 구현을 염두하고 배치 및 연결되기 때문에 이 과정이 끝나면 반도체 칩의 면적을 알 수 있어야 한다. 물리적 설계 공정이 끝나면 레이아웃 형태의 칩은 실리콘 위에 올라가 실제 칩으로 양산된다.

반도체 회로 설계 공정은 1) 논리적, 2) 물리적 수준으로 나뉜다. 마찬가지로 반도체IP는 논리적 수준인 Soft IP와 물리적 수준인 Hard IP로 나뉜다. Soft IP는 HDL를 합성해 게이트 수준 회로로 나타내는 과정에 사용된다.

Soft IP는 RTL 수준의 알고리즘으로 존재한다. CPU, GPU 등 프로세서가 어떻게 작동하는지를 나타내는 아키텍처 혹은 Controller 같이 작업처리를 결정하는 스케줄링 기능이기 때문에 코드 형태로 존재하는 것이다.

반면 Hard IP는 회로 내 칩 간 소통, 칩과 외부 디바이스의 연결 등 회로의 물리적 배치와 연결을 다루기 때문에 실물 형태로 존재한다. Hard IP는 실물로 존재 한다는 특성 때문에 파운드리가 바뀌거나 공정이 미세화될 때 Soft IP와 달리 새로 IP를 만들어야한다. Soft IP 대비 파급 속도가 비교적 더딘 편이다.

Hard IP는 물리적 집적회로 형태로 판매되지만 Soft IP는 RTL 수준 코드가 판매 되기 때문에 기술력이 노출될 우려가 있다. 이를 방지하고자 IP업체들은 암호화 한 코드를 고객사에게 전달하며 고객사는 결과값만 받아 IP를 활용하는 방식이다.

4. 반도체IP 종류

반도체IP 종류는 기능에 따라 세 가지로 나뉜다. CPU, GPU, AP 등 연산장치와 관련된 Processor IP, 칩 내외부 장치간 연결을 돕는 Interface IP, 그리고 논리 게이트 등 설계의 기초가 되는 Foundation IP를 의미한다. 이 외에도 쓰임새에 따라 카메라 코덱 IP부터 보안용 IP까지 다양한 종류의 IP가 있다.

스마트폰의 출시부터 포화까지 Core, GPU, Memory가 결합된 AP SoC(System on Chip)의 수요가 폭발적으로 증가했다. 따라서 Processor IP의 성장률이 가팔랐으며 시장 점유율 대부분을 차지하게 됐다.

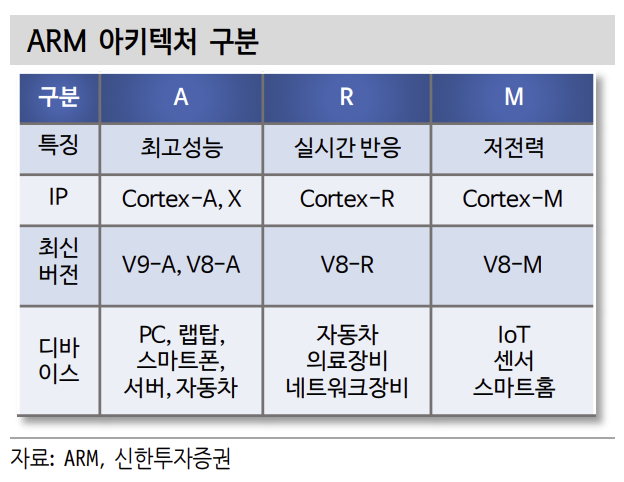

Processor IP는 사실상 ARM 아키텍처가 독과점 중이다. 스마트폰부터 자동차, TV, PC, 노트북, 서버까지 대부분 디바이스에 들어간다. 2022년 기준 ARM의 매출액은 28억달러이며, IP 시장 M/S는 40%로 추정한다.

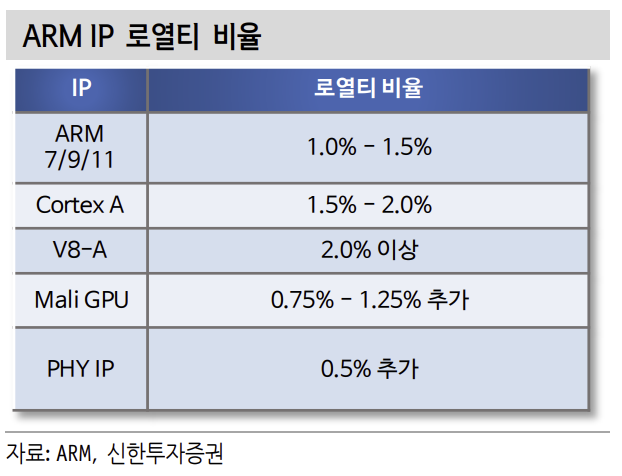

IP 가격대는 기술 수준에 따라 다양하다. 인터페이스 혹은 아날로그 등 기술적 정교함이 비교적 낮은 IP는 라이선스 가격이 20억원 미만이지만, ARM v8-A 같 이 AP 혹은 노트북용 칩으로 쓰이는 프로세서 IP는 100~130억원으로 추정된다.

Interface IP는 활용처에 따라 Memory(DDR, LPDDR, GDDR, HBM), Mobile/PC(USB, MIPI, SATA, eMMC/SD), Networking(SerDes, Ethernet), Display(HDMI/DP), Server/Storage(CXL/CCIX, PCIe), Chiplet(D2D, UCIe)로 나뉜다. AI 반도체와 NPU 성장으로 데이터 간 고속 연결이 중요해졌기 때문에 Interface IP 향후 성장률은 Processor IP 보다 높을 것으로 추정한다.

Interface IP의 경우 고속 연결과 직결되는 High end IP(PCIe, DDR, Ethernet, D2D, MIPI)가 70~90억원에 달한다. 반면 기술개발이 성숙단계에 이른 Low end IP(USB 등)가 15~20억원에 거래된다.

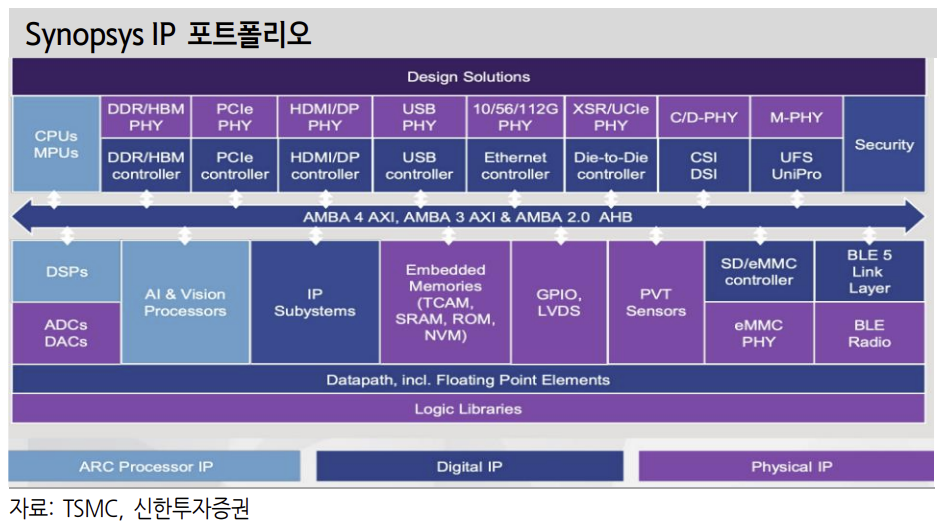

Interface IP는 사실상 Synopsys와 Cadence가 과점 중이다. Synopsys는 High end 부터 Low end IP를 모두 갖고 있다. 또한 Processor IP도 보유하고 있기 때문에 IP 시장 M/S 20%로 ARM에 이은 2등 사업자이다. 반면 Cadence는 고속 연결 관련 High end Interface IP위주로 M/S 6%의 3등 사업자이다.

Interface IP 산업 시장은 1) 선단 공정, 2) 고 단가 IP 위주 경쟁이 치열해지고 있 다. 공정이 미세화될수록 EDA Tool부터 장비, 인건비 등 제반 개발비용이 상승 하기 때문에 IP 가격이 오른다. 고속 연결을 중심으로 하는 PCIe, DDR, D2D, MIPI의 판매가는 높을 수밖에 없다.

최근 IP업체 간 경쟁은 선단 공정 고속 연결 IP 위주로 발생했다. 따라서 신생 IP 기업은 1) 레거시 공정 일반 연결 IP, 2) 과점사 대비 20~30% 할인된 첨단 공정 고속 연결 IP를 공급하여 시장의 빈틈을 공략 중이다.

반도체IP 시장규모는 반도체IP사 매출액 합산으로 추정한다. 2022년 기준 75억달러로 추정한다. 2020년~2023년까지 3년간 CAGR 16.8% 성장했다. 2023년 ~2025년 CAGR 성장률은 16.6%로 2025년 102억달러를 전망한다.

5. 반도체IP BM 분석

반도체IP사는 팹리스 혹은 파운드리 수요로 매출을 인식한다. 매출 유형은 1) 라이선스 수익, 2) 로열티 수익 두 가지다. 팹리스는 새로운 칩을 개발할 목적으로 개발 시작 시 IP사를 찾는다. 파운드리는 고객사를 위해 대응가능한 IP 포트폴리 오 확장 차원에서 IP사와 계약한다. 파운드리를 대신해 DSP사와도 거래한다.

칩 개발은 통상 1.5~2년이 걸린다. IP사는 1차적으로 개발 시작 시 라이선스 매 출을 인식하고, 2차적으로 칩이 팔리기 시작할 때 로열티 매출을 인식한다. 로열티 매출은 칩 판매 시 개당 정액 혹은 정률 방식으로 산정한다. 칩 개발과 양산의 시차를 고려할 때 업력이 오래될수록 로열티 매출 비중이 높 다. 업계 M/S 1위 ARM의 로열티 매출액 비중은 130~180%이다. 반면 M/S 3 위 Cadence는 18~23%로 로열티 매출 비중이 높지 않다.

업력 외 Hard/Soft IP 포트폴리오 분포 차이도 존재한다. Processor IP 중심 ARM과 달리 Synopsys는 Interface IP 위주 매출액 비중이 크다. Interface IP는 크게 PHY(Physical, 회로 물리적 구현)와 Controller(PHY를 통제하는 역할)로 나뉜다. 이때 PHY는 Hard IP이고 Controller는 Soft IP이다.

Hard IP는 실제 회로인 물리적 결과물을 제공한다. 따라서 로열티 보다 라이선스 매출을 크게 잡는다. 반면 Soft IP는 RTL 수준의 논리적 회로이기 때문에 칩 판매 시 로열티 매출이 더 많이 발생한다. 따라서 Hard IP 비중이 높은 Synopsys 는 Soft IP 위주인 ARM 대비 로열티 매출액 비중이 낮다.

출처: 신한투자증권, ARM, 오픈엣지테크놀로지, TSMC, 삼성전자

뜨리스땅

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체IP 투자포인트 (0) | 2023.09.22 |

|---|---|

| 반도체 기술 탐구: 반도체 IP 산업에 대한 분석 (0) | 2023.09.21 |

| Apple, TSMC 그리고 삼성전자의 삼각 관계 1 (0) | 2023.09.12 |

| 반도체 기술 탐구: CoWoS와 InFO (0) | 2023.09.05 |

| 반도체 기술 탐구: MR-MUF (몰디드 언더필) 기술 개발(feat. by 헨켈) (1) | 2023.08.29 |

댓글