1. CoWoS란 무엇인가?

CoWoS는 2.5D 패키지 기술을 의미하는 TSMC의 브랜드명으로, 2개 이상의 반도체 칩을 웨이퍼 상에서 상호 연결한 뒤 패키지 기판에 올린다는 뜻이다. 따라서 CoWoS 역시 기존 2.5D 패키지 기술의 특성을 그대로 가지고 있다.

2.5D 패키지의 의미는 2D 패키지처럼 칩이 수평 방향으로 배열되면서도, 3D 패키지와 마찬가지로 속도 제한 없는 상호 연결이 가능한 패키지라는 뜻으로, 인터포저가 사용되면, 인터포저 위에 메모리와 로직 반도체를 평면으로 놓기도 하고, 수직으로 쌓기도 하여 2D와 3D가 합쳐진 형태로 구현되기 때문이다.

CoWoS가 구현되기 위해서는 각 칩을 마치 하나의 다이처럼 연결해주는 실리콘 인터포저 기술이 핵심적이다. 인터포저는 substrate(기판)의 일종이지만 어떠한 로직 기능 없이 신호 연결만을 담당하는 게 특징으로, CoWoS뿐 아니라, 최근 잘 알려진 HBM에서도 필수적인 부품 및 기술이다.

인터포저는 기존의 패키지 기판 대비 미세 회로 구현이 가능해 2.5D 패키지 내에서 각 칩을 연결하는데 사용된다. 다만 대면적으로 갈수록 가격이 비싸다. 두께가 100μm(마이크로미터) 수준으로 얇아 제조상 컨트롤하기도 어렵다.

TSMC는 팬아웃-웨이퍼레벨패키지(FoWLP) 기술에 속하는 ‘InFO’와 함께 CoWoS를 3차원 구조(3D Fabric)로 분류하고 있다. 또 CoWoS 내에서 각 칩을 어떤 방식으로 연결하느냐에 따라 ‘CoWoS-S’, ‘CoWoS-R’, ‘CoWoS-L’ 3 단계로 구분한다.

이번에 TSMC가 애플 M1 울트라 제조에 사용한 기술은 이 중에 CoWoS-S로, 각 칩 연결에 풀사이즈 인터포저만을 사용하는 방식이다. CoWoS-S는 데이터 통신 속도는 가장 빠르지만 대면적 인터포저 탓에 제조단가는 가장 비싸다.

2. CoWoS의 종류

애플의 M1 울트라는 CPU⋅GPU가 10코어⋅32코어인 M1 맥스 2개를 이어 붙여 정확히 두 배씩의 성능을 구현했다. 20코어 CPU, 64코어 GPU로 내장 트랜지스터는 총 1140억개이며, D램은 총 128GB(기가바이트)를 탑재할 수 있다. 칩간 대역폭은 1초당 2.5TB(테라바이트)에 달한다. 애플은 CPU 성능 면에서 M1 울트라가 인텔 28코어 CPU를 탑재한 맥 프로보다 최대 60% 더 빠르다고 밝혔다.

이에 비해 CoWoS-R과 CoWoS-L은 CoWoS의 가성비 버전이다. CoWoS-R은 고가의 인터포저 대신 재배선층(RDL)을 배치해 칩들을 연결하는 방식이다. 통신 속도는 CoWoS-S 대비 느리다.

CoWoS-L은 칩 전체를 덮는 풀사이즈 인터포저 대신 로컬실리콘인터커넥트(LSI, Local Silicon Interconnect)라는 소형 인터포저를 사용한다. 칩과 칩을 연결하는 부위에만 브릿지 타입의 소형 인터포저를 배치한다.

인텔의 최신 패키지 기술인 EMIB(Embedded Multi-Die Interconnect Bridge)도 여기에 속한다.

한 반도체 후공정 업체 임원은 “M1 울트라는 CoWoS-S를 통해 물리적으로 완벽하게 연결하기도 했지만, 소프트웨어적으로도 한 개의 다이처럼 움직이게 구현한 게 혁신”이라고 설명했다.

3. CoWoS의 발전 history

기술이 발전하면서 인터포저 크기도 늘어나고 있다. 2012년 TSMC가 처음으로 이 기술을 소개했을 때 인터포저 면적은 800㎟에 불과했다. 지난 2020년에 발표한 인터포저 면적은 1700㎟나 된다. 약 8년 새 면적이 2배 이상 늘어나, 더 많은 칩을 올릴 수 있게 된 것이다. 또 초기에는 28나노 칩에 대응할 수 있는 기술로 출발했지만 이제는 5나노 칩도 대응할 수 있다.

TSMC 측은 “새로운 CoWoS 기술은 2개 로직 시스템온칩(SoC) 다이와, 96GB 고대역폭(HBM) 메모리 6개를 올릴 수 있다”며 “이 공법은 초당 2.7테라바이트 대역폭을 제공하는데, 2016년 TSMC가 가지고 있던 CoWoS 솔루션보다 2.7배 빨라진 것”이라고 밝혔다.

메모리와 로직 반도체 간 연결성을 극대화한 이 기술은 고성능 컴퓨팅 시스템 업계에서 주목받을 것으로 예상된다. TSMC는 메모리 칩이 유용하게 쓰이는 딥러닝, 5G 네트워크 인프라, 데이터센터 업계 등에서 이 기술이 각광받을 것으로 예상했다.

4. CoWoS와 동반자: InFO

TSMC는 CoWoS와 함께 통합팬아웃(InFO) 기술로 패키징 기술 확장을 노리고 있다. 칩의 배선을 밖으로 빼내서 패키징을 하는 기술인데, 2016년부터 애플 칩의 팬아웃 패키징을 싹쓸이 하면서 패키징 업계 주도권을 잡은 바 있다.

초박형 패키지 InFO는 두께가 불과 0.5mm밖에 안되며, 기판이 없어 재료비를 줄일 수 있고, 웨이퍼 레벨의 대량 생산으로 제조 비용을 줄이는 뛰어난 패키지 기술이다.

TSMC는 InFO는 모바일 디바이스를, CoWoS는 고성능 컴퓨팅용에 구분하여 적용하려는 전략을 수립해왔다.

InFO (Integrated Fan-Out WLP)의 개념은 실리콘 다이의 외부 패키지에서 입출력 단자의 영역을 넓힌 것이 특징이다. 외부 공간에서 1,000핀 이상의 입출력 단자를 처리할 수 있도록 지원, 멀티 다이를 탑재하고 수동 소자를 넣을 수 있게한 패키지이다.

실리콘 다이의 입출력 패드에서 패키지의 입출력 단자로 출력 신호를 재배치하는 고밀도 배선층은 RDL(Re-Distribution Layer)이라 부르며 박막 공정에서 형성된다.

위의 InFO와 CoWoS를 비교한 것을 보면, 어떤 차이가 있는지 알 수 있다. 세로 축은 입출력 단자의 수, 가로 축은 패키지의 면적이다. 따라서, InFO는 모바일용 소형 패키지에, CoWoS는 고성능 컴퓨팅을 위한 대형 패키지에 적용된다는 것을 알 수 있는 차트이다.

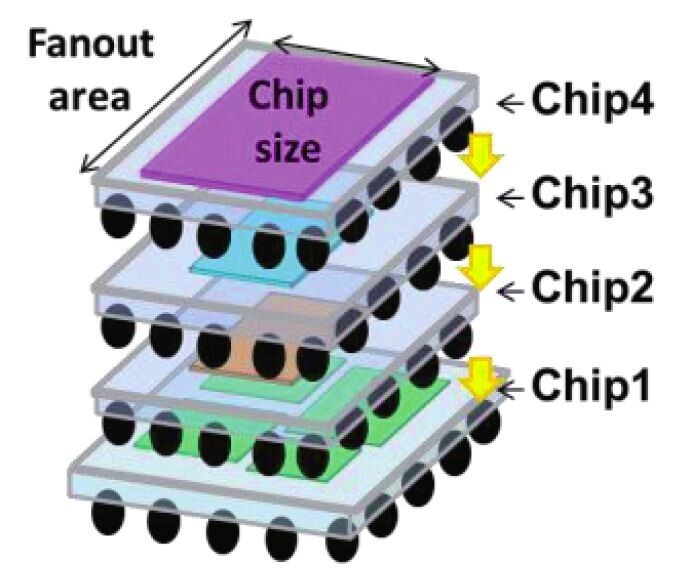

VLSI 기술 심포지엄에서 TSMC는 InFO을 상하로 적층하는 스택형 InFO 패키지 기술을 밝혔다. 적층 수는 4층을 상정했는데, 2층은 지금의 InFO 기술로도 커버 가능하며, 8층은 제조 기술 난이도가 높아진다.

출처 : KIPOST, 기글 하드웨어, 전자신문

뜨리스땅

https://tristanchoi.tistory.com/458

반도체 기술 탐구: SK Hynix의 HBM 패키징 기술, TSV와 MR-MUF

1. TSV HBM 기사가 나오면 단골손님처럼 등장하는 기술 용어가 'TSV'이다. TSV는 'Through Silicon Via'의 줄임말로 실리콘(반도체 wafer)를 관통하는 만드는 배선, 즉 '실리콘관통전극'이다. 반도체의 집적도

tristanchoi.tistory.com

https://tristanchoi.tistory.com/515

삼성전자와 SK하이닉스의 HBM 접근 방법

1. SK하이닉스의 HBM은 MR-MUF로 HBM은 2013년 12월 SK하이닉스가 세계 최초로 개발한 이후 HBM2→HBM2e→HBM3→HBM3e로 개발되어 왔다. HBM을 적층하는데 있어 SK하이닉스는 HBM2까지는 NCF(Non Conducted Film)를 사

tristanchoi.tistory.com

https://tristanchoi.tistory.com/511

반도체 기술 - HBM 공정 순서

1. TSV 중심 전반 요약 2. 세부 공정 별 순서 1) Silicon Etch: 실리콘을 식각하여 깊은 트렌치(trench, 구멍)를 형성하는 공정 FEOL 공정 이후 웨이퍼를 식각하여 트렌치를 만드는 공정이다. 식각 공정에

tristanchoi.tistory.com

https://tristanchoi.tistory.com/277

반도체 기술 탐구: 차세대 패키지 기술 종합 2 - 인터포저

1. 인터포저의 정의 인터포저(Interposer)는 복수 칩 결합을 위해 사용되는 패키지 기술 중 하나로, 피치(Pitch) 차이가 큰 반도체 칩(Semiconductor Chip)과 기판(Substrate)를 전기적으로 연결하기 위해 삽입

tristanchoi.tistory.com

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체 기술 탐구: 반도체IP의 이해 (1) | 2023.09.20 |

|---|---|

| Apple, TSMC 그리고 삼성전자의 삼각 관계 1 (0) | 2023.09.12 |

| 반도체 기술 탐구: MR-MUF (몰디드 언더필) 기술 개발(feat. by 헨켈) (1) | 2023.08.29 |

| 전자 부품 기술 탐구: 초전도체 LK99에 대한 논란 5 (feat. by Science) (0) | 2023.08.27 |

| 반도체 기술 탐구: AI 시대에 주목받은 메모리 반도체 HBM (2) | 2023.08.27 |

댓글