1. SK하이닉스의 HBM은 MR-MUF로

HBM은 2013년 12월 SK하이닉스가 세계 최초로 개발한 이후 HBM2→HBM2e→HBM3→HBM3e로 개발되어 왔다. HBM을 적층하는데 있어 SK하이닉스는 HBM2까지는 NCF(Non Conducted Film)를 사용하는 열 압착 방식의 TC-NCF 방식을 사용해왔다. HBM2e부터는 MR-MUF 공정으로 대체하게 되었고 HBM3, HBM3e까지 이어지고 있다. 에스티아이는 MR-MUF공정에 사용되는 Reflow 장비를 HBM3부터 공급하고 있다.

MR(Mass Reflow)은 기존에 플립칩(Flip Chip)에서 서브스트레이트와 패키지의 솔더볼을 접착해주는 공정에 사용되었다. 플럭스(Flux)를 서브스트레이트의 패드에 올리고 Reflow 공정으로 솔더볼을 녹여 붙인 후 플럭스를 세척하여 제거하는 방식이다.

적층과 미세화가 진행되면서 MR 공법은 TC(Thermal Compression) 공법으로 전환되었고, SK하이닉스의 HBM1과 HBM2는 TC-Bonder를 활용한 TC-NCF 방식으로 생산하였다. 다만 열압착 방식은 본딩할 때마다 일정 시간 동안 열과 압력을 주어야 해서 전체 공정 시간이 길어 생산성이 낮다는 단점이 있다. SK하이닉스는 HBM2e부터는 MR-MUF(Mass Reflow-Molded Underfill) 방식으로 생산한다. 삼성전자와 Micron은 TC-NCF 방식을 사용한다.

MR-MUF 공정은 마이크로 범프를 부착한 칩에 플럭스를 도포하여 적층하고 대량의 마이크로 범프를 한번에 녹여 칩과 회로 간 연결한다. 이후 칩과 칩 사이에 에폭시 밀봉재를 주입하여 언더필(Udnerfill) 작업과 함께 외부로 부터 보호하는 몰딩(Molding)까지 동시에 진행하게 된다.

12단 HBM3 제품에는 Advanced MR-MUF 기술이 적용된다. Advanced MR-MUF는 마이크로 범프를 부착한 칩에 금속 결합물질을 도포하여 적층한다. 이후 칩 하나를 쌓을 때마다 순간적으로 높은 열을 가열하고, 칩이 휘는 현상을 방지하기 위해 범프와 패드를 임시 접합하게 되며 칩을 1층씩 적층할 때마다 반복한다.

임시로 접합된 범프와 패드에 Reflow를 통해 적층된 칩을 한꺼번에 완전 접합하고 방열 효과가 더욱 높은 신규 에폭시 밀봉재를 주입하여 칩을 외부 충격으로부터 보호한다. 칩 공간 사이에 채워진 신규 에폭시 밀봉재와 칩을 완전히 접합하기 위해 열과 압력을 가해 굳혀서 HBM을 완성하게 된다. 기존 MR-MUF 대비 생산성은 약 3배, 열 방출은 약 2.5 배 개선을 이루었다.

MR-MUF 방식은 TC-NCF와 달리 칩간 Gapfill 소재(NCF)를 범프로 고온, 가압 관통시킬 필요가 없다. 대기 상태로 본딩함으로 Chip Warpage 제어와 Gapfill-MUF 소재가 핵심 기술이며, 이를 통해 기존 공법 대비 수율과 품질 향상을 이루었다.

TC-NCF 공정을 사용하지 않더라도 열과 압력을 가하는 공정에는 TC-Bonder가 계속 사용된다. 다만 TC-NCF와 달리 MR-MUF에서는 Reflow의 중요도가 높아진 것이 차이점이라 판단된다. 에스티아이의 Fluxless Reflow 장비가 퀄을 통과할 시 HBM3e에는 기존 Flux Reflow와 함께 사용될 것으로 예상된다.

SK하이닉스는 HBM 경쟁력을 지속하기 위해 HBM CAPA를 기존 대비 2배 이상 확대시킬 계획이다. HBM3부 터 사용된 동사의 Reflow 장비는 HBM3e에도 지속적으로 사용될 예정이다. SK하이닉스의 신규 HBM CAPA 투 자는 HBM3 및 HBM3e 중심으로 될 것으로 예상되기 때문에 HBM3부터 공급하고 있는 동사의 Reflow 장비 매출은 CAPA 증설 규모 대비 클 전망이다.

2026년 하반기에 양산될 것으로 예상되는 HBM4에는 Hybrid Bonding이 적용될 것으로 보이나 16단이 아닌 8 단 및 12단에서는 여전히 MR-MUF 공법이 사용될 것으로 보인다. 또한 HBM3 시장을 선점하고 있는 SK하이 닉스의 HBM 경쟁력은 Nvidia내 높은 점유율을 바탕으로 당분간 지속될 것으로 예상한다. 2022년 전체 HBM 시장에서 SK하이닉스의 시장점유율은 약 50%로 2023년과 2024년에도 49% 수준을 유지할 것으로 전망된다. 따라서 동사의 Reflow 장비 수요는 중장기적인 관점에서도 긍정적이라 판단된다.

2. 삼성전자 인프라 투자는 지속

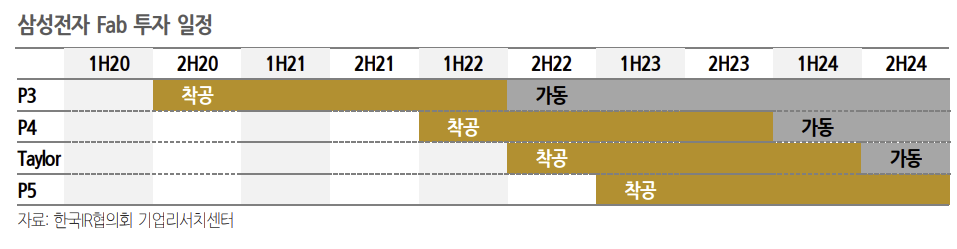

삼성전자는 반도체 업황 둔화로 인해 신규 CAPA 투자는 매우 부진한 상태이다. 하지만 삼성전자는 장비투자 금액을 크게 축소시키는 한편 신규 Fab과 R&D는 지속적으로 투자하고 있다. 이는 중장기 공급성을 적기에 확보하기 위한 것으로 P3와 P4 중심으로 인프라 투자가 진행 중이다.

상반기에는 P3의 Phase3 및 Phase4 인프라 투자가 있었고 Phase4 투자는 하반기에도 이어질 것으로 예상된다. P4의 경우 당초 예상보다 진행 속도가 다소 지연되고 있어 4분기부터 유틸리티 투자가 시작될 것으로 보인다. 미국 Taylor Fab 투자 역시 예정대로 진행 중이다.

출처: 한국IR협의회, AMD

뜨리스땅

https://tristanchoi.tistory.com/458

반도체 기술 탐구: SK Hynix의 HBM 패키징 기술, TSV와 MR-MUF

1. TSV HBM 기사가 나오면 단골손님처럼 등장하는 기술 용어가 'TSV'이다. TSV는 'Through Silicon Via'의 줄임말로 실리콘(반도체 wafer)를 관통하는 만드는 배선, 즉 '실리콘관통전극'이다. 반도체의 집적도

tristanchoi.tistory.com

https://tristanchoi.tistory.com/511

반도체 기술 - HBM 공정 순서

1. TSV 중심 전반 요약 2. 세부 공정 별 순서 1) Silicon Etch: 실리콘을 식각하여 깊은 트렌치(trench, 구멍)를 형성하는 공정 FEOL 공정 이후 웨이퍼를 식각하여 트렌치를 만드는 공정이다. 식각 공정에

tristanchoi.tistory.com

https://tristanchoi.tistory.com/277

반도체 기술 탐구: 차세대 패키지 기술 종합 2(인터포저란 무엇인가?)

1. 인터포저의 정의 인터포저(Interposer)는 복수 칩 결합을 위해 사용되는 패키지 기술 중 하나로, 피치(Pitch) 차이가 큰 반도체 칩(Semiconductor Chip)과 기판(Substrate)를 전기적으로 연결하기 위해 삽입

tristanchoi.tistory.com

https://tristanchoi.tistory.com/477

반도체 기술 탐구: CoWoS와 InFO

1. CoWoS란 무엇인가? CoWoS는 2.5D 패키지 기술을 의미하는 TSMC의 브랜드명으로, 2개 이상의 반도체 칩을 웨이퍼 상에서 상호 연결한 뒤 패키지 기판에 올린다는 뜻이다. 따라서 CoWoS 역시 기존 2.5D 패

tristanchoi.tistory.com

'반도체, 소.부.장.' 카테고리의 다른 글

| 2024 반도체 시장 전망 1 - 2023년은 Downcycle의 마무리 구간 (0) | 2023.11.18 |

|---|---|

| 반도체 기업 탐구: 텔레칩스 (0) | 2023.11.17 |

| 반도체 기업 탐구: 에스티아이 (1) | 2023.11.12 |

| 2023 2H 반도체 장비 업체 시황 점검 - 2/2 (0) | 2023.11.08 |

| 2023 2H 반도체 장비 업체 시황 점검 - 1/2 (0) | 2023.11.07 |

댓글