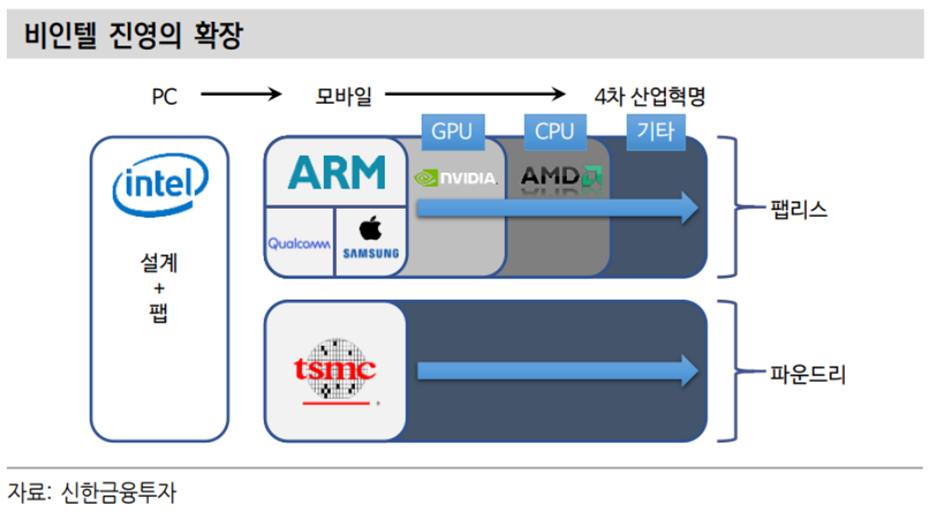

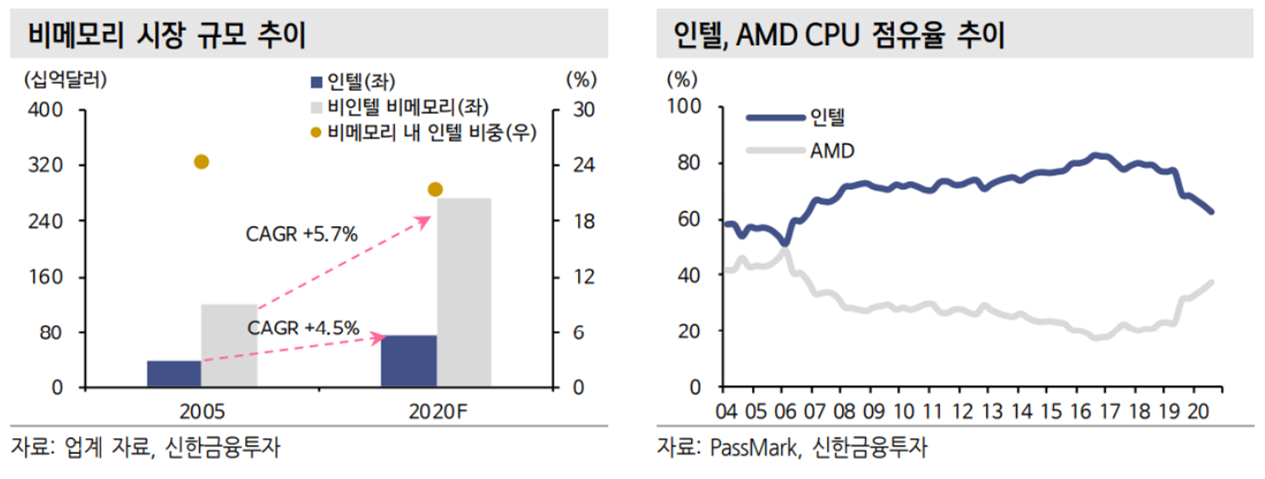

인텔의 7nm 지연 뉴스는 비메모리 산업 전망에 매우 큰 이슈다. 비메모리 시장 은 인텔과 비인텔 진영으로 이분화할 수 있는데, 비인텔 진영의 확장 기회로 해석되기 때문이다.

비메모리 Foundry는 중요한 기술 변화를 앞두고 있다. 전공정 3nm 선폭부터 기존 FinFET 공정 적용으로는 누설전류 제어가 어렵다. Foundry 업체들은 FinFET 공정을 개선한 GAA(Gate All Around) 공정을 도입할 전망이다. 후공정에서도 TSV(Through Silicon Via) 등 부가가치 향상 경쟁이 본격화될 전망이다.

1. 비인텔 진영의 확장 기회

비메모리 Foundry 시장은 2010년 초반부터 급격히 성장해 왔다. 비메모리 시장 은 인텔 영역(IDM)과 비인텔 진영(Fabless, Foundry 분업)으로 이분화할 수 있다.

① 인텔이 모바일 시대와 4차 산업혁명에 대한 준비가 늦어지면서, 모바일 AP와 GPU에서 경쟁력을 발휘하지 못했다.

② 또한 14nm 이후 10nm 공정기술 개발이 지연되면서 기존에 독점하다시피했던 CPU 시장에서도 M/S를 잃게 되었다.

이는 Fabless 업체들과 Foundry 업체들의 급격한 성장으로 연결되었다.

이 추세는 장기간 지속될 전망이다. 인텔이 7nm 공정 개발이 지연되고 있기 때 문이다.

비메모리 Foundry 업체들은 Fabless 업체 또는 세트 업체들이 원하는 스펙으로 제작하여 제공할 역량을 갖추고 있어야 선택 받을 수 있다. 모든 측면에서 압도적인 TSMC는 시장 장악력을 유지 또는 상승시킬 전망이다. 그리고 2 nd tier 중에서 전공정 기술과 후공정 기술이 앞서 있는 삼성전자가 고성장 Foundry 시장에서 M/S를 상승시킬 것으로 기대된다.

2. 전공정 GAA와 후공정 TSV 적용

Fabless 업체들의 성장 기회는 그대로 Foundry 업체들에게 연결될 수 밖에 없다. 말 그대로 Fabless 업체들은 팹이 없기 때문이다. 인텔의 헤게모니 훼손과 비인텔 진영의 시장 확장 구간에서 Foundry 업체들은 더 큰 파이를 차지하기 위해 경쟁하고 있다.

Foundry 업체는 고객들의 칩 요구 성능을 높여 주어야 한다. 비 메모리 칩 성능개선은 통상적으로 속도 증가, 전력소모량 감소, 기타 성능 개선 등이 요구된다.

이를 위한 Foundry 업체들의 핵심 역량은 ① 납기 대응력, ② 전 공정 기술, ③ 후공정 기술 등 크게 세가지로 요약된다.

① 납기대응력

Foundry 업체들은 자체적으로 IP 또는 셀 라이브러리를 보유하고 있다. Fabless 업체는 Foundry 업체로부터 IP 또는 셀 라이브러리를 제공받아 설계하고, DB를 Foundry 업체에게 다시 보내게 된다. Foundry 업체는 설계 DB를 Fab에서 제작 후 Fabless 업체에게 보내고, Fabless 업체는 세트 업체에게 판매한다.

이때 다양한 다양한 IP 또는 셀 라이브러리를 보유하고 있는 Foundry 업체들은 고객 주문에 유기적으로 빠르게 대응할 수 있는 기회가 있다. 고객이 칩 제작을 요구할 때, 다른 기술력 또는 조건이 동일할 경우 납기 대응력이 높은 Foundry 업체를 선택하는 것은 당연할 수 밖에 없다. Foundry 업체들 중에서 TSMC가 IP 보유에서 절대적으로 앞서 있는 것으로 파악된다. TSMC는 GUC 등 주변 업체 들과의 Supply Chain 형성도 긴밀하게 형성되어 있어 유리하다.

② 전공정 기술

Fablss 업체가 더 짧은 선폭의 공정기술을 Foundry 업체에게 요구하는 이유는 Transistor 사이 전자 이동 거리가 짧으면 반도체 속도가 빨라지기 때문이다. 짧은 선폭을 전공정 기술로 구현할 수 있는 Foundry 업체가 고객의 선택을 받기 유리하다. 전공정 기술에서 TSMC가 삼성전자보다 앞서고 있는 것은 사실이나, 삼성전자가 TSMC와 거의 대등한 수준까지 따라온 것으로 판단된다.

삼성전자는 10nm 공정까지 TSMC와 대등한 전공정 기술을 확보했었다. 다만, 7nm 공정에서 EUV 적용을 선택한 삼성전자는 EUV 없이 개발한 TSMC보다 늦었다. ASML의 EUV 장비 개발 및 공급 시점이 생각보다 늦었기 때문이다. 그러나 5nm 공정부터 삼성전자가 TSMC와 대등한 시점에 양산을 시작했다.

언론 보도에 의하면, 삼성전자는 5nm 공정을 적용하여 퀄컴의 스냅드래곤 875, 스냅드래곤 X60을 양산할 예정이다. 그리고 삼성전자는 지난 2Q20 실적발표에 서 5nm 양산 착수 및 4nm 공정 개발을 진행하고 있다고 언급했다.

반도체 핵심 소자인 Transistor를 구현할 때, Foundry 전공정에 요구되는 것은 처리 속도를 증가시키고, 소비전략을 감소시키는 것이다. Transistor의 선폭이 좁 아지면, 누설전류(Leakage Current)가 발생하여 Short Channel Effect가 발생한다. 누설전류가 발생할 경우, 전력소모량이 많아진다. 현재까지 Foundry 업체들은 HKMG(High-k Metal Gate)와 FinFET 공정을 적용하여 기술을 개발해 왔다. 14nm 선폭부터 적용되어 온 FinFET 공정이 4nm 미만 선폭에서는 한계를 보일 가능성이 높다.

그래서 Foundry 업체들은 GAA(Gate All Around) 공정을 적용할 전망이다. 언론 보도에 의하면, 삼성전자는 3nm 선폭부터, TSMC는 3nm 또는 2nm부터 GAA 공정을 적용할 계획이다. GAA 공정 기술 개발을 먼저 성공하는 업체가 대형 고객들에게 수주를 선점할 전망이어서, GAA가 본격 적용될 2021-22년이 Foundry 시장에 변곡점이 될 가능성 높다.

GAA를 적용하는 이유는 FinFET과 동일하다. 두 공정 모두 Transistor의 전류가 이동하는 소스와 드레인 사이에 구조를 개선하여 접촉 면적을 늘리고(속도를 증 가시키고), 물고기 지느러미 모양처럼 쥐어짜게 만들어 누설전류를 최소화하는 접근이다. GAA는 FinFET보다 전류가 이동하는 접촉 면적이 넓고 전류가 흐르는 채널 4면을 Gate가 둘러싸고 있다. FinFET보다 채널 조정 능력을 추가적으로 개 선시킨 방법이다.

GAA는 Transistor 구조를 전면적으로 변경하는 것이기 때문에, 공정 기술상 많 은 어려움이 등장할 것으로 전망된다. 구조 변화로 인해 Vth(Threshold Voltage) 등 Transistor Engineering이 매우 어려워 진다. 최적의 Transistor 조건을 찾기 위해 상당한 연구 개발 기간이 필요하다. 또한 소스 및 드레인 영역에 pit 또는 hole이 발생할 가능성이 높고, Dry Etch시 PR(Photo Resist)이 마스크 역할을 제 대로 수행하기 어려워 Patterning 난이도가 상승할 것이다.

삼성전자는 GAA 기술을 오랜 기간 동안 준비해 온 것으로 파악된다. 삼성전자 가 많은 난제들을 해결하고 공정 기술 개발에 성공할 경우, 거대 고객들의 수주 를 받을 수 있는 기회가 될 수 있다.

③ 후공정 기술

비메모리 시장에서 후공정은 OSAT(Outsourced Semiconductor Assembly and Tect) 업체들이 담당하고 있다. 패키징, 테스트 등 후공정 기술은 난이도가 전공 정 대비 훨씬 낮고 반도체 성능 개선에 크게 기여하지 못했기 때문에 부가가치 가 상대적으로 낮다. 그래서 Foundry 업체들은 전문 OSAT 업체들에게 후공정 을 외주로 맡기고 있다.

그런데 F/O(Fan Out)과 TSV(Through Silicon Via) 등 신규 후공정 기술 도입으 로, 후공정으로도 큰 폭의 반도체 성능 개선이 가능해졌다. 이에 TSMC 또는 삼 성전자가 직접 F/O 또는 TSV 등 후공정 기술을 내재화하여 부가가치를 상승시 킬 수 있다. Foundry 업체들이 후공정 기술에 직접 관여하여, 수주 경쟁에 기회 로 활용하거나 더 높은 가격을 책정 받으려고 노력할 전망이다.

F/O 또는 TSV는 전공정이 완성된 반도체 칩에 추가적으로 고성능, 고용량, 저 전력화를 더할 수 있다. TSV가 궁극적인 기술로 예상되며, F/O은 TSV 기술이 완성되기 전 최상위 후공정 기술로 평가된다. TSV가 양산이 본격화되면 F/O은 차상위 기술로 포지션될 전망이다.

TSV가 본격화되기 전 비메모리 시장에서는 후공정 기술로 F/O을 요구하고 있 다. 상대적으로 TSV 대비 공정 난이도가 낮기 때문이다. F/O을 구현하는데 TSMC와 삼성전자는 다른 방법을 선택했다. TSMC가 WLP(Wafer Level Package) F/O으로, 삼성전자는 PLP(Panel Level Package) F/O으로 개발을 시도했다. 그리고 TSMC가 WLP F/O로 양산화에 먼저 성공했고, 애플의 A 시리즈 칩을 독점 수주할 수 있었다.

WLP F/O과 PLP F/O은 접근 방법이 다를 뿐 최종 목적은 동일하다. 고객이 요구한 성능을 맞춰준다면, 고객 입장에서 WLP와 PLP를 구분할 필요는 없다. WLP와 PLP는 Foundry 업체들이 선택할 문제다. WLP F/O은 일반적인 반도체 전공정에서 활용하는 기술을 유사하게 도입하기 때문에 공정의 개발 속도가 빠를 수 있다.

PLP F/O은 원형인 Wafer 위에서 적용 하는 기존 반도체 공정과 다르게, 직사각형인 Panel 위에서 적용하기 때문에 새로운 접근이 필요하다. 이에 공정 개발 완성 시점이 다소 늦어질 수 있는 불리함 이 있다. 반면 PLP F/O은 기술을 완성했을 경우, 대량으로 면적 손실 없이 생산 할 수 있기 때문에 Foundry 업체 이익에 유리할 수 있다.

삼성전자는 초기 PLP 개발 과정에서 고객 선점 기회를 놓쳤고, 작년부터 삼성전 기로부터 PLP F/O 사업부를 가져왔다. 삼성전자가 F/O 양산 기술을 완성하는 시점에 TSMC와 대등한 기회를 고객들에게 제공받을 수 있다.

최근 삼성전자는 3차원 적층 패키지 기술인 ‘X-Cube(eXtended-Cube)를 적용 한 테스트칩 생산에 성공했다. 로직과 SRAM을 단독으로 제작 후 TSV 기술로 적층한 것이다. 데이터 처리 속도를 증가시켜 슈퍼컴퓨터, 인공지능, 5G 등 고성 능 시스템 반도체를 요구하는 분야는 물론 스마트폰과 웨어러블 기기의 경쟁력 을 높일 수 있는 핵심 기술로 활용될 전망이다.

다만 이미 전공정이 완성되어 비용 처리가 완료되었고 당장 판매할 수 있는 반도체 칩들에 대해 추가적인 공정을 진행하는 것이기 때문에, 완성도 높은 TSV 수율 확보가 반드시 필요하다. TSV가 궁극적인 후공정 기술로 오랜 기간 평가받 아 왔지만 아직 본격적으로 양산화되지 못하고 있는 이유다.

TSV 공정은 궁극적으로 비메모리, 메모리 등 구분 없이 적층하는 방식으로 적용 할 전망이어서, 종합 반도체 업체에게 유리하다. 메모리와 비메모리를 대규모 양 산하는 업체는 전세계에 삼성전자가 유일하다. TSV의 기술 진입장벽이 높은 만큼, 삼성전자가 TSMC 대비 TSV 양산을 선점할 경우 Foundry 시장에서 M/S를 크게 상승시킬 수 있는 기회가 될 전망이다.

3. 마무리

삼성전자의 비메모리 Foundry 사업부는 매우 빠른 성장이 전망된다.

① 4차 산업혁명으로 비인텔 영역이 확장되면서 Foundry 시장 성장의 수혜가 예상된다. 그리고

② GAA 공정 도입을 통한 전공정 기술력, F/O 또는 TSV 공정 도입을 통한 후공정 기술력으로 2 nd tier 중에서 독보적인 경쟁력을 확보하여 M/S를 지속 상승시킬 전망이다.

시간이 더 필요하겠지만, IP 또는 셀 라이브러리를 강화하는 시점부터는 TSMC와 대등한 경쟁을 할 수 있다.

출처: 신한금융투자, 삼성전자, Digitimes, Passmark, Trendforce, TSMC

뜨리스땅

구독과 공감, 댓글은 힘이 됩니다.

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체 기업 탐구: 원익QnC (0) | 2020.10.01 |

|---|---|

| SMIC 제재에 따른 파운드리 시장의 영향 (0) | 2020.09.28 |

| 반도체 기술 탐구: NAND의 기술 변화 (0) | 2020.09.06 |

| 반도체 기술 탐구: EUV 두번 째 이야기 (0) | 2020.09.06 |

| 반도체 기업 탐구: 기술변화에 따라 영향 받는 기업들 (0) | 2020.09.06 |

댓글