전 세계적으로 반도체 업계의 초미세 공정 경쟁이 거세진 가운데 유럽 최대 반도체 나노기술 연구소 IMEC의 1나노미터(nm) 반도체 기술 공정 로드맵이 업계 눈길을 끌고 있다.

IMEC는 반도체 설계부터 공정, 소자, 시험, 제작 등 모든 공정의 연구개발(R&D)을 지원하는 네덜란드, 벨기에, 프랑스 합작의 반도체 종합연구소다. 현재 약 100개국과 공동연구 중이다.

역사를 돌아보면 주요 단계별 대표적 공정기술과 이에 따른 기술적 진보는 꽤 재미있다.

인텔은 반도체 시장 초기부터 불과 몇 년 전까지만 해도 꽤 잘나가는 기업이어서, 초기의 공정기술은 인텔이 주도했다. 1971년 세계 최초의 마이크로프로세서인 인텔 ‘4004’ 프로세서의 미세공정 수준은 10㎛(마이크로미터, 미크론)로, 이것도 머리카락과 비교하면 불과 10분의 1밖에 안되는 수준이다.

이런 미세공정을 인텔은 수년에 한 번씩 개선해 1989년 486 프로세서에서는 마침내 1㎛ 미만의 시대로 접어들었으며, 이후 6년 만인 1995년 펜티엄 프로부터는 드디어 지금의 나노 시대로 접어들게 된다. 당시 수준은 350㎚.

나노화가 이뤄진 뒤에도 미세공정 수준은 놀라울 정도로 빠르게 향상됐다. 인텔은 1997년 100㎚를 더 줄여 250㎚를 달성하더니, 2012년에는 다시 10분의 1 수준인 22㎚까지 도달했다. ‘반도체 미세공정의 한계는 과연 어디까지일까?’란 기대감이 끊이질 않던 시기이기도 했다.

하지만 이런 인텔도 2014년 14㎚ 이후론 사실상 무릎을 꿇은 모양새다. 그다음 세대인 10㎚ 공정 개발에는 성공했으나 이를 상용화하진 못해 사실상 시장 경쟁권에서 밀려나고, 현재 10㎚ 이하의 전쟁은 한국의 삼성전자와 대만의 TSMC가 주도하고 있다.

이 중 TSMC는 전통의 ArF(불화아르곤) 공정으로 먼저 7㎚ 시대를 열며 삼성을 앞서는 듯했으나, 차세대 핵심 전장인 5㎚ 이하 양산에서는 EUV(극자외선) 도입에 오랜 시간 공들인 삼성의 다소간 우세가 점쳐지는 상황이다.

하지만 미세공정 수준만 높이는 것도 점점 한계에 이르고 있다. 특히 극도로 미세화된 회로가 항공 운송 중 방사선의 영향을 받아 불량이 발생하는 수준에까지 이른 지금은, 미세화는 물론, 운송과 불량 발생 관련 문제 등을 보완하기 위한 기술 역량의 요구 역시 중요해지고 있는 시기다.

최근의 28나노 이후의 로드맵은 지난해 10월 IMEC 주최로 일본 도쿄에서 열린 'IMEC 테크놀로지 포럼 재팬 2019(ITF 재팬 2019)'의 나명희 IMEC 부사장 강연을 통해 잘 알 수 있다.

나 부사장은 2019년부터 IMEC에 합류해 반도체 미세 공정 및 부품 R&D 부문을 총괄하고 있다. 그는 과거 IBM에서 18년간 근무하면서 최첨단 반도체 공정 연구에 주력해 왔다. 당시 나 부사장은 ‘반도체 공정 미세화를 향한 길’이라는 주제 강연에서 28나노부터 1나노까지 IMEC의 반도체 공정 전체 로드맵을 제시했다.

나 부사장은 강연에서 반도체 칩이 미세화, 집적화할수록 공정의 복잡성 때문에 제조비용이 올라가기 때문엔 트랜지스터 1개당 제조비용을 기대한만큼 내리기 힘들며 이로써 ‘무어의 법칙’을 따라잡는 게 어려워졌다고 했다. 무어의 법칙은 반도체 내 트랜지스터 수가 2년마다 갑절로 늘어나 칩 처리능력이 2배로 향상된다는 법칙이다.

나 부사장은 이처럼 무어의 법칙이 이미 통하지 않은 지는 오래됐지만, IMEC는 포기하지 않고 트랜지스터 구조와 재료를 지속적으로 개선하는 한편, 공정의 최적화를 통해 1나노까지 달하는 기술 로드맵을 제시했다고 밝혔다.

1) 28나노 공정은 HKMG(하이K메탈게이트) 공정을 적용하며,

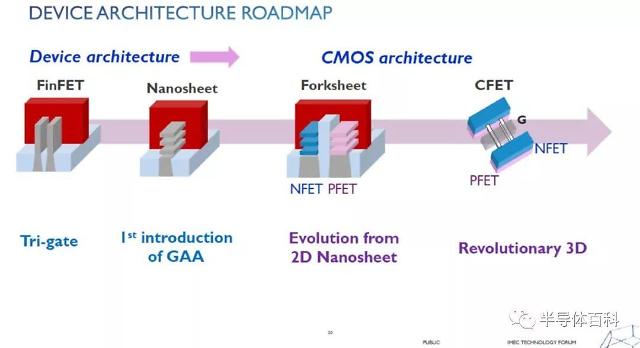

2) 14~16나노부터는 전통적인 평면 구조에서 핀펫(Fin-FET) 구조 공정으로 생산한다. 핀펫 공정은 평면 구조 한계를 넘기 위해 도입된 기술로, 위·좌·우 3면만을 게이트로 쓰는 3차원 방식이다. 채널 모양이 지느러미(Fin)를 닮았다고 해서 붙은 이름이다.

3) 이어 5~7나노 공정부터는 노광·식각·증착 공정(MOL)에서 일산화탄소(Co)를 배선재료로 채택하고 극자외선(EUV) 리소그래피(노광) 장비를 통해 핀펫 구조를 더욱 세밀화한다.

4) 그리고 3~4 나노 공정부터는 핀펫이 게이트올어라운드(GAA, Gate-All-Around) 구조로 대체됐다. 위·좌·우 3면만을 게이트로 쓰는 핀펫과 달리 아랫면까지 모두 쓰는 4차원 방식이다. 1세대 GAA는 실리콘 나노시트를 적용했다.

5) 나 부사장은 2나노 공정부터는 핀펫 구조의 물리적 한계를 극복하기 위해 한층 업그레이드 된 포크시트(Forksheet) 구조를 기반으로 한다고 설명했다. 포크시트란, N형 펫(FET, 전계효과트랜지스터)과 P형 펫의 나노시트가 긴밀히 붙어있고, 이 가운데 ‘절연벽’이란 게 존재하는데, 바로 이것을 가리키는 용어다. 절단면이 포크와 유사하다고 해서 붙여진 이름이다.

6) 그리고 1나노 공정에서는 CFET(The Complementary FET) 공정을 채택한다. 여기에서는 P형 펫 위에 N형 펫을 쌓는 방식이다. 즉 서로 다른 전도 유형의 트랜지스터를 교대로 3차원적으로 쌓아 셀 면적을 크게 감소시키는 것이다. 또 여기에 ‘하이(High)-NA’EUV 노광 공정을 통해 트랜지스터 구조를 한층 더 축소할 수 있다.

나 부사장은 IMEC는 또 2차원적 재료와 스핀트로닉스(전자 자전학), 그리고 양자 컴퓨팅을 도입하는 방안도 검토 중이라고 밝혔다. 고도의 미세 공정을 위해 설계와 공정의 동시 최적화(DTCO) 이외에도 시스템과 공정의 동시 최적화(STCO)도 중요하다는 게 그의 설명이다.

나 부사장은 기존의 정적램(SRAM)은 각 메모리 셀 평면을 5개 트랜지스터로 구성해야 했지만, IMEC는 트랜지스터 구조와 전력선을 개선하는 방식으로 SRAM 트랜지스터의 수를 각 메모리셀 당 4.4개까지 줄일 수 있다고 강조했다. 사실상 SRAM의 면적 단위를 3분의 2 수준으로 줄인 셈이다.

아울러 나 부사장은 무어의 법칙을 연장할 수 있는 또 다른 기술로 3D 패키징도 함께 언급했다.

그는 IMEC가 현재 수직적 적층과 수평적 미세 공정을 동시에 연구해 시스템 집적도를 높이기 위해 노력하고 있다고 말했다. 이를 위해 공정기술, 설계기술, 시스템 기술 최적화에도 주력한다는 계획이다.

출처: 아주경제, 테크월드

뜨리스땅

https://tristanchoi.tistory.com/53

파운드리 공정 기술 경쟁 : 3나노를 향한 승부수

1. 주요 업체들의 최근 동향 반도체 위탁생산(파운드리) 업계의 나노 경쟁이 심화되고 있다. 삼성, TSMC, SK하이닉스, 글로벌 파운드리 등이 주요 업체이지만, 7나노미터(nm)부터는 대만 TSMC와 삼성

tristanchoi.tistory.com

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체 공정 기술: EUV는 어디에 쓰나? DRAM vs. 파운드리 (0) | 2020.06.30 |

|---|---|

| 파운드리 공정 기술 경쟁 : 3나노를 향한 승부수 (0) | 2020.06.30 |

| 반도체 소재 기업 탐구: 이엔에프테크놀로지 (0) | 2020.06.28 |

| 반도체 소재 기업 탐구: 솔브레인 (0) | 2020.06.28 |

| 반도체 시장 메카니즘: 업황, 주가, 가격 (0) | 2020.06.26 |

댓글