1. 기업 개요

네패스는 1990년 12월에 반도체 및 전자관련 부품 전자재료 및 화학 제품 제조 판매를 영위할 목적으로 설립된 후, 1999년 12월 코스닥에 상장된 기업으로 동사는 종속회사 및 계열회사로 이루어진 15개의 계열회사를 보유하고 있다.

네패스는 우리나라 반도체 산업과 그 역사를 함께 한다. 1990년 네패스 전신인 크린크리에이티브가 설립된 후 2년 만에 반도체·디스플레이용 미세회로 형성용 현상액을 첫 국산화했다. 초기에는 화학 소재 사업에 집중했다.

2000년대 들어 창업자인 이병구 네패스 회장은 새로운 도전에 나섰다. 바로 시스템 반도체 패키징 사업에 나서 본격적인 반도체 산업에 뛰어든 것이다. 당시 국내에는 시스템 반도체, 그 중에서 첨단 패키징 기술은 굉장히 생소한 영역이었다. 네패스는 시스템 반도체 고성능화가 이뤄지면서 패키징 기술 중요성이 부각될 것이라고 예견하고 본격적인 사업화에 나섰다.

2000년 회사 내 반도체사업부를 신설하고 2001년 당시 150억원을 투자해 충북 오창에 부지 3000평 규모 패키징(플립침용 범프) 생산라인을 구축했다. 20년이 지난 지금 네패스의 반도체 부문은 계열사 포함 전체 매출의 83%를 차지할 정도로 핵심 사업으로 부상했다.

동사의 연결대상 종속회사는 네패스아크, 네패스라웨와 그 종속기업인 네패스야하드, 네패스엘이디, nepes hayyim, nepes Energy holdings Ltd., nepes US,Inc., PT.NEPES ABADI INDONESIA, nepes Hokmah 등이다.

2. 주요 사업 부문 및 기술

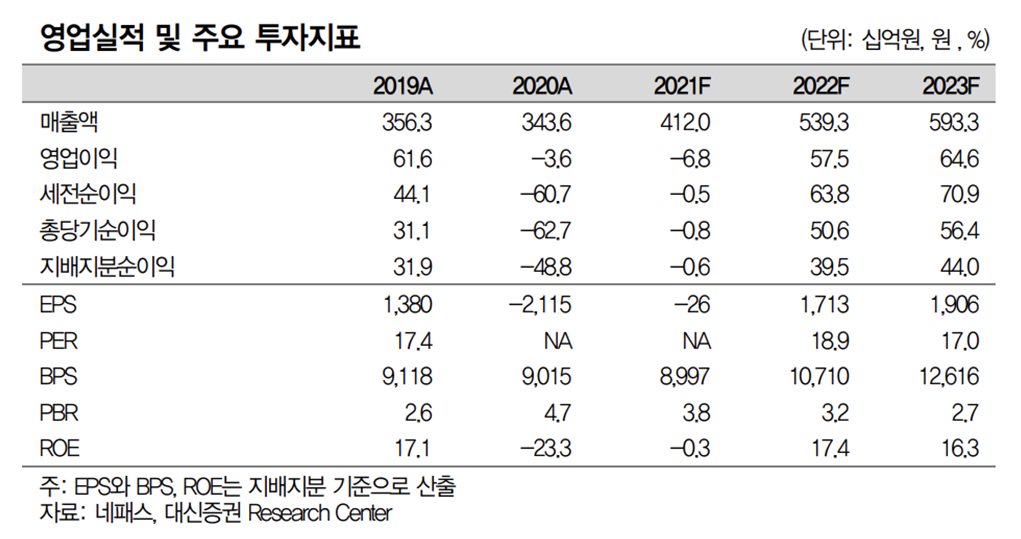

주요 사업부문은 시스템반도체(비메모리 반도체)의 후공정 분야로 WLP, FOWLP/PLP, SiP, 테스트 등으로 구성되어 있고 엔드팹 기술을 턴키 베이스로 공급하여 첨단 백엔드 파운드리 사업(파운드리 사업 위한 후공정)을 영위하고 있다. 수요처와의 공동개발 및 중장기양산 계획을 공유하며 안정적 고객 및 공급처를 확보하고 있다.

2.1. 후공정

최근 비메모리 반도체 밸류 체인에서 후공정의 중요성이 더욱 높아지고 있는데, 이는 크 게 두 가지 측면으로 나눠볼 수 있다. 하나는 기술적으로 갖는 중요성이며, 다른 하나는 비메모리 반도체 제조 생태계 구축과 관련된 내용이다.

우선 시스템 반도체 후공정의 전반적인 절차는 다음과 같다.

후공정 중에서도 가장 핵심이 되는 공정은 단연 패키징이라고 할 수 있으며, 후공정이 갖는 기술적 중요성 역시 대부분 패키징의 영역에서 비롯된 것이다. 전공정이 반도체 칩 자체의 성능을 끌어올리는 과정이라면, 후공정은 그렇게 끌어올린 칩의 성능을 효율적으 로 뽑아낼 수 있게 가공하는 과정이다. 이러한 가공의 핵심이 바로 패키징 공정이다.

따라서 외부로부터 칩을 보호하고 전기적 통로를 연결하는 전통적인 역할을 넘어선 패키징 기술이 필요하다. 또한 전공정에서의 기술 발전은 이미 상당 부분 진행된 상태이므로, 패키징 기술 발전을 통해 높아진 칩의 성능이 실제 제품의 퍼포먼스로 이어질 수 있도 록 만드는 것이 매우 중요한 과제이다.

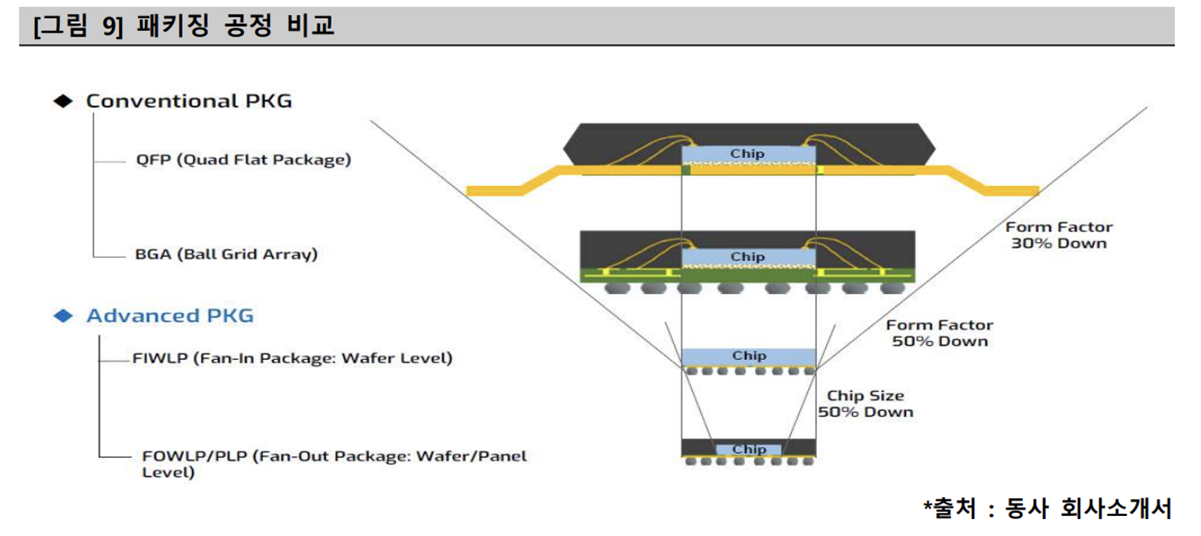

이러한 기술적 요구를 충족시키기 위해 패키징 방식은 발전을 거듭해왔다. 이로 인해 패키징 방식을 Legacy와 Advanced로 나누는 경우가 많은데, Advanced 패키징 시장의 규모가 빠르게 증가하고 있다.

특히 패키징 공정의 원가 절감과 관련하여 WLP(=FI-WLP, FI) 방식이 주목을 받아왔으며, 최근에는 반도체 칩의 미세화, 집적도 증가 등의 트렌드에 걸맞은 방식으로서 Fan-out 패키징 방식이 주 목을 받고 있다. FI와 FO는 각각 7%와 15%라는 높은 매출액 CAGR 수치를 보이고 있다.

후공정 업체의 경우 패키징 방식의 발전과 관련된 기술적 역량을 갖추는 것도 중요하지만, 그 기술을 실제로 적용하여 유의미한 실적을 내고 있는지 여부도 중요하다.

특히 국내 주요 비메모리 반도체 생산 업체들이 주력하는 제품이 PMIC, DDI, CIS라는 점을 고려할 때, 발 전된 패키징 기술을 바탕으로 국내 반도체 생산 업체들로부터 해당 제품들의 패키징 분 야에서 인정받는 업체, 실제로 매출을 발생시키고 있는 업체가 앞으로 후공정 생태계 구축에 있어 중요한 역할을 맡을 것으로 전망된다. 미래 전망의 관점에서 본다면 전방의 반도체 생산 업체들이 RF나 차량용 반도체 부문 등에서 경쟁력 확대를 도모하고 있으므 로 해당 분야의 패키징을 담당하는 업체의 역할도 확대될 것으로 보인다.

동사의 주력으로 매출의 80%를 차지하고 있는 반도체 사업부문은 웨이퍼 레벨 패키지 이하(‘WLP’), FOWLP, FOPLP, 테스트 등으로 구성되어 있다. 그 외 전자재료 사업부문은 제조공정용현상액 칼라 필터용 현상액 세정제 연마제 등의 제품으로 구성되어 있으며 이차전지 사업부문은 이차전지용 리드탭 등이 있다.

WLP 방식은 현재 동사의 주요 매출원으로, 이 방식을 통해 국내 최대 비메모리 생산 업체인 삼성전자의 PMIC와 DDI 부문의 제1 협력사로서의 지위를 차지하고 있다. 또한 앞 으로 패키징 기술의 Paradigm Shift를 이끌 Fan-out 패키징 분야에서는 국내 업체 중 유 일하게 생산 기술을 보유하고 있다.

최근 반도체 패키징에 쓰이는 PCB 공급 부족으로 전례 없는 대란이 벌어지고 있으며 이에 동사는 2021년 6월에 온라인으로 열린 글로벌 전자부품 전시회 2021 전자부품 및 기술박람회(ECTC)’ 에서 인쇄회로기판(PCB)를 배제한 SiP(SYSTEM IN PACKAGE) 기술을 공개했다.

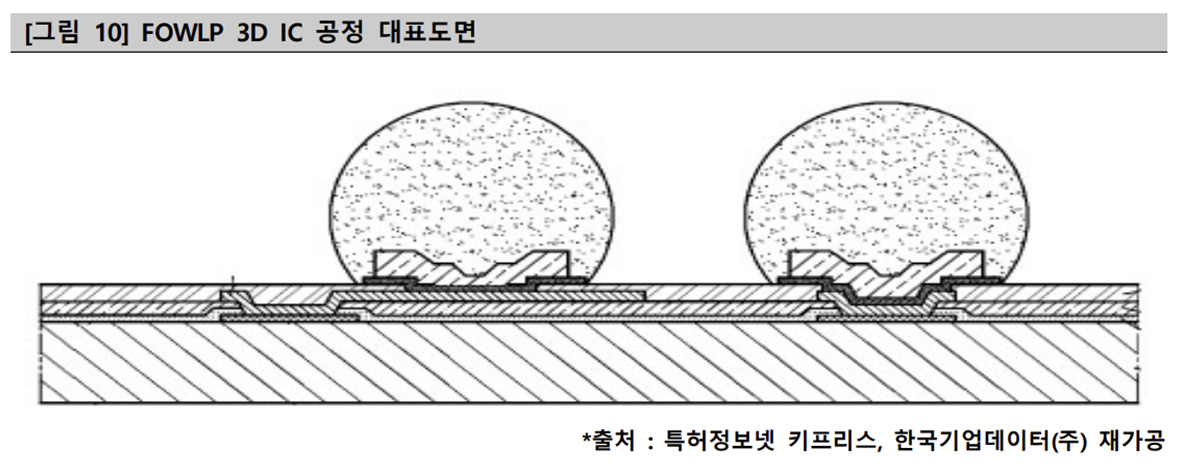

동사는 칩의 바깥으로 재배선 및 범핑을 확장하여 다수의 I/O를 지닌 칩을 미세패키징을 진행하여 빠른 신호전달 속도와 높은 퍼포먼스로 고성능IC FOWLP, FOPLP 를 제조할 수 있는 기술을 지속적으로 개발하고 있다. 또한 IoT, 자율주행 등 디바이스 고사양화로 시스템반도체의 기술변화를 촉구하고 있는 가운데 차세대 뉴로모픽 반도체에 적용할 수 있는 FOWLP 기술을 개발하고 있다.

동사가 개발하고 있는 FOWLP 기술은 젖음성이 우수한 커버층(주석, 납, 은, 금 등의 혼합 화학물질 을 형성시키고, 리플로우 공정을 진행하여 두꺼운 접착층을 만들어 패드 근방 크랙 발생을 억제하여 칩과 기판과의 접합도를 향상시킨 공정 기술과 FOWLP 3D IC 를 적용할 수 있는 멀티 칩 SiP 내부 로직 IC와 IPD(고성능 반도체 파워 스위치) 구조와 뉴로모픽 반도체를 접합하고 증착 패터닝 할 수 있는 기술을 개발하여 기술경쟁력을 강화해나가고 있다.

네패스는 끊임없는 연구개발(R&D)과 인프라 투자로 패키징 기술을 선도하는 기업이 됐다. 특히 팬아웃(FO) 분야에 압도적 우위를 자랑한다. 팬아웃은 반도체 다이 밖까지 재배선층(RDL)을 확장시켜 반도체 칩의 신호 입출력(I/O)을 늘리는 기술이다. 전력 효율성을 크게 높이고 칩의 신호 처리 능력도 개선할 수 있다. TSMC가 삼성으로부터 애플 칩 생산을 가져올 수 있었던 것도 이 팬아웃 기술 때문으로 알려졌다.

네패스의 팬아웃 패키징은 자회사인 네패스라웨와 네패스하임이 담당한다. 네패스는 팬아웃 패키징에 힘을 싣기 위해 2020년 2월 네패스라웨를 물적 분할했다.

네패스 강점은 첨단 팬아웃 패키징 기술에 있다. 팬아웃웨이퍼레벨패키징(FO-WLP)과 팬아웃패널레벨패키징(FO-PLP)이다.

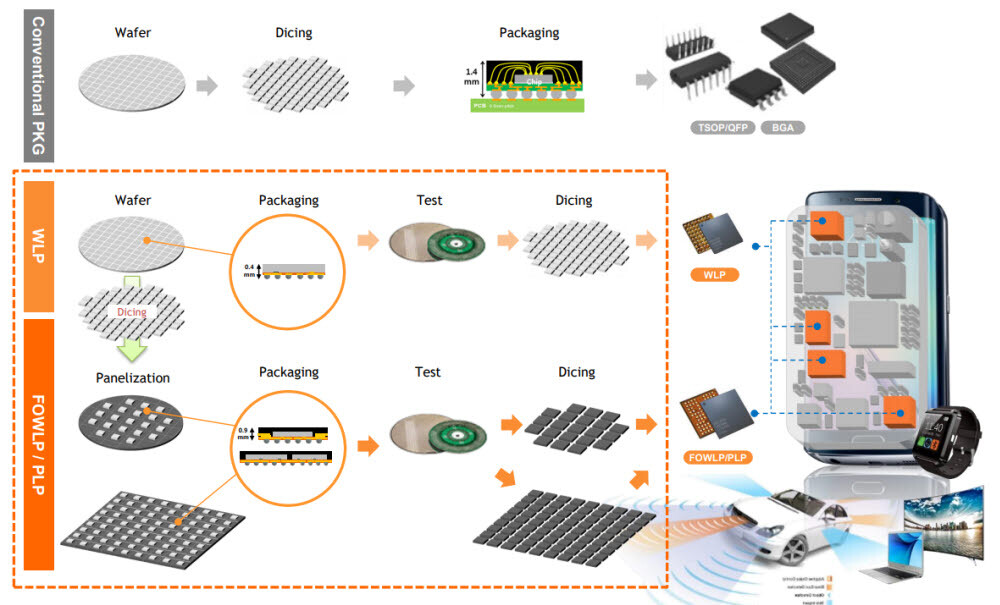

전통적인 패키징은 웨이퍼에 회로를 그려 반도체 다이를 만든 후(전공정), 웨이퍼를 개별 다이로 자른다. 이를 다시 패키징 기판에 범핑해 연결하는 방식이다. 공정 과정이 여러 단계고 패키징 기판이 필요해 시간과 비용이 많이 들었다.

이런 제약을 극복하기 위한 것이 웨이퍼레벨패키징(WLP)이다. WLP는 웨이퍼에 바로 RDL를 형성해 공정 과정을 줄인다. 또 웨이퍼에서 바로 패키징하기 때문에 패키징 기판을 사용하지 않는다. 비용 절감 효과뿐만 아니라 칩을 가볍고 얇게 만들 수 있다. 네패스에서 물적 분할한 네패스라웨가 글로벌 전장부품 업체에 FO-WLP을 제공하고 있다.

네패스는 한발 더 나아가 FO-PLP까지 상용화했다. PLP는 웨이퍼에 직접 패키징하는 WLP와 달리 반도체 다이를 사각형 패널에 배치해 패키징하는 기술이다. 원형에서 패키징하는 것보다 생산성은 높이고 비용을 줄일 수 있다. 네패스는 가로, 세로 각각 600mm 크기 사각 패널을 사용하는데 300mm(12인치) 웨이퍼 대비 장당 5~6배 많은 반도체를 생산할 수 있다. 보통 PLP는 WLP 방식보다 생산성이 96% 높은 것으로 알려졌다.

세계에서 FO-PLP 기술을 가진 회사는 네패스와 삼성전자, ASE, 파워텍, JCET 등이 있다. 네패스는 FO-PLP 패키징 설비 등 인프라 구축에 2019년 말부터 2000억원 이상을 투자했다. 충북 괴산군 청안에 약 6만평 규모 패키징 공장을 세웠다. 현재 양산 준비 단계로 알려졌다.

글로벌 팹리스 업체의 전력관리반도체(PMIC) 패키징에 FO-PLP를 적용하기 위한 성능 테스트를 진행 중이다. 최종 양산 승인을 받으면 PMIC에 FO-PLP를 적용한 세계 첫 사례가 될 전망이다.

2.2. PMIC 위한 후공정

네패스 패키징 매출 가운데 PMIC와 디스플레이구동칩(DDI)가 절반이다. PMIC는 네패스의 주력이기도 하다. 국내 주요 고객사의 PMIC를 패키징, 테스트하고 있다. 최근 정보기술(IT) 기기가 고사양화하면서 효율적인 전력 관리를 위한 PMIC 채택이 늘고 있다. 스마트폰에서 PMIC 침투율이 높은데, 롱텀에벌루션(LTE) 스마트폰 대비 5세대(5G) 이동통신 스마트폰에서 PMIC가 2~3개 더 많이 쓰일 것으로 전망된다. 5G 스마트폰 시장이 크게 성장하고 있어 네패스 패키징 사업에는 호재다.

PMIC는 Power Management IC의 약자로, 전자기기의 심장 역할을 하는 파워소자이다. 전자기기의 각 부분에 필요한 전력을 정확하고 효율적으로 공급/관리해주는 역할을 맡고 있다. 배터리가 전력을 보관하는 저수지의 역할이라면, PMIC가 배터리로부터 필요한 전 력을 적재적소로 이동시킨다. 즉, PMIC는 충전이 필요한 전자기기에는 반드시 탑재되어 야 하는 핵심 반도체라고 할 수 있다.

이러한 PMIC는 기능에 따라 여러 종류로 나뉘는데, 대표적으로 SoC PMIC, 충전 기능의 PMIC, 그리고 디스플레이 PMIC로 나뉜다. 전자기기의 두뇌 역할을 하는 SoC PMIC에서 는 CPU, GPU, NPU, 그리고 모뎀까지 내장되어 있어 상황 별로 서로 다른 전력을 공급할 수 있게끔 한다. 두 번째로, PMIC는 전자기기의 충전 및 고속 충전을 담당한다. 과거에 비해 배터리 용량이 2~3배 이상 늘어났지만, 충전 시간이 줄어들 수 있는 이유는 PMIC 가 더 많은 전력을 공급할 수 있도록 발달된 덕분이다. 충전 기능과 관련하여 PMIC는 기기 간의 통신도 지원하는데, 전자기기의 배터리 잔량을 체크하고 이를 스마트폰에 전 달하는 기능을 담당한다. 마지막으로, 디스플레이 PMIC에서는 주변 환경에 따라 화면의 밝기를 효율적으로 조절하는 역할을 담당한다.

각자 다른 기능을 수행하는 여러 종류의 PMIC가 존재하는 것에서 알 수 있듯이, PMIC는 하나의 기기에 여러 개가 탑재된다는 특징을 가지고 있다. 고성능의 전자기기일수록 더 많은 개수의 PMIC가 필요하다. 예를 들어, 통상적으로 스마트폰에는 최소한의 기능을 가진 스마트폰에 3~4개가 탑재되며, 고성능 스마트폰으로 갈수록 더 많은 개수가 탑재 된다.

2.3. DDI 위한 후공정

동사의 두 번째 주력 제품인 DDI는 Display Driver IC의 약자이다. DDI는 OLED, LCD 등의 디스플레이를 구성하는 수많은 픽셀을 구동하는 데 쓰이는 작은 반도체 칩이다. 디스플 레이가 화면에 정보를 표현하기 위해서는

1) 사용자가 터치나 리모컨을 통해 기기를 컨트롤 해야 한다.

2) 이 명령을 기기의 두뇌에 해당하는 AP, CPU 같은 중앙처리장치가 신 호로 처리해서 내보낸다.

3) 이 신호가 PCB를 통해 DDI로 전달되며, DDI는 디스플레이 패널 상 각각의 RGB 픽셀이 어떻게 행동하라는 명령을 TFT를 조절하면서 전달한다. 즉, DDI는 AP와 패널 사이 통로의 역할로, 픽셀들의 ‘신호등’에 해당하는 반도체이다.

DDI의 후공정은 크게 Bumping, Probe test, 조립 공정, 그리고 Final test로 나뉜다. 그 중 동사는 Bumping부터 조립 공정까지는 물론이고, 최근에는 Final test까지 수행하는 Turn Key 수주를 확대하고 있다.

DDI는 종류가 크게 2개로 나뉘는데, 스마트폰, 모바일 등 소형 기기에 들어가는 것과, 태블릿, 스마트TV 등 중대형 전자제품용으로 나뉜다. 일반적으로 스마트폰에는 기기 당 1개의 DDI가 탑재되며, 중대형 전자제품에는 최대 48개까지 탑재된다.

이러한 DDI의 성장성은 OLED에서 찾을 수 있다. 스마트폰에 OLED 패널이 탑재될수록 DDI에 높은 성능이 요구된다. OLED 패널의 탑재와 동시에 스마트폰의 테두리에 해당하 는 베젤이 얇아지는 기술에 있어서 DDI 기술이 중요하게 작용하기 때문이다. OLED 패널 은 LCD와 달리 패널 뒤의 백라이트가 사라지기 때문에 뒤로 휘어진다는 특징이 있다. DDI는 패널의 위 혹은 아래에 붙어있었는데 OLED 도입으로 패널에 붙은 DDI를 뒤로 휘 어서 넘길 수 있게 되었고, 이것이 얇은 베젤(테두리)를 가능하게 하였다. OLED 기술도 물론 구현하기 어렵지만, 이것을 지원하는 DDI 기술도 난이도가 있다.

동사의 최대 고객사인 삼성전자는 DDI 분야에서 17년째 전 세계 1위를 달리고 있다. 스 마트폰 4대 중에 한 대는 삼성전자의 DDI를 사용하고 있으며, 특히 전 세계 OLED 스마 트폰 중에서는 95%의 점유율을 차지하고 있다. 따라서 동사의 DDI는 글로벌 OLED 스마트폰에 대한 전망과, 삼성디스플레이의 OLED TV 전망을 통해 성장성을 살펴볼 수 있을 것이다. 스마트폰과 TV 시장 역시 COVID19로 인해 타격을 받지만, OLED 스마트폰과 TV 출하량은 꾸준히 성장할 전망이다. 그만큼 OLED가 차지하는 비중이 높아지고 있다는 뜻이다.

3. 전략적 투자 진행 내역

자회사 '네패스라웨'가 1000억원 규모의 유상증자를 단행하고, 차세대 공정 FO-PLP(팬아웃패널레벨패키징) 생산능력(CAPA) 확대에 나섰다. 내년부터 본격적으로 FO-PLP 양산구간에 진입하는 고객사 물량에 대응하기 위해서다. IPO(기업공개) 시계도 돌아가기 시작했다는 관측이 나온다.

네패스라웨는 3자배정 유상증자 방식으로 전환우선주(CPS) 408만주를 발행, 총 1000억원의 시설자금을 조달한다. 에스지프라이빗에쿼티(SG PE)가 운용하는 블라인드펀드(에스지코어 유한회사)에서 400억원, 한투PE와 공동 조성한 구조혁신펀드(한투에스지제이호유한회사)에서 400억원, 에스케이에스한국투자제1호 사모투자합자회사에서 200억원을 투자했다. 이번 유상증자에선 4500억원가량의 기업가치가 책정됐다.

네패스라웨는 삼성전자의 차세대 패키징 공법인 FO-PLP에 특화된 패키징 하우스다. 비메모리 파운드리 시장에서 경쟁하는 대만 TSMC의 FO-WLP와 차별되는 공정이다. 삼성전자와 네패스라웨는 웨이퍼 단위로 패키징을 하는 방식에서 벗어나 600x600mm 사각패널에 일괄 패키징하는 방식으로 공정을 이원화해 생산효율을 대폭 끌어올린다는 방침이다. 둥근 형태의 웨이퍼 레벨 패키징 대비 버려지는 웨이퍼가 대폭 줄어들고, 양산속도도 크게 올라간다. 생산량 역시 웨이퍼 레벨 대비 5배 이상 늘어난다.

2200억원가량을 투자해 최근 괴산 청안공장을 준공한 네패스라웨는 기초 설비투자가 완료된 직후 이번 1000억원 투자를 통해 FO-PLP 시장의 우위를 점하겠다는 복안이다. 업계에선 이번 증설투자를 FO-PLP '1차 케파업(CAPA UP)'으로 평가하고 있다.

이번 생산능력 확대는 궁극적으로 미국 주요 고객사 향 패키징 대응에 맞춰져 있다. 정확한 고객사의 명칭은 양사간 NDA(비밀유지협약)에 따라 공개하지 않았다. PMIC(전력반도체), SoC(시스템온칩) 등 비메모리 설계 부문의 글로벌 톱티어로, 삼성전자와 더불어 네패스그룹의 최대 고객사다. 대량 PO(구매주문) 협의가 오가면서 고객사의 증설 요청이 있었던 것으로 파악된다.

박찬호 현대차증권 연구원은 “네패스의 주요 성장 동력인 팬아웃-패널레벨패키지(FO-PLP)사업은 기존 전망대로 올해 상반기 생산 안정화에 들어가고 하반기부터 본격적으로 가동률이 높아질 것”이라고 전망했다.

출처 : 테크월드뉴스, 조선비즈, 전자신문, SMIC

뜨리스땅

https://tristanchoi.tistory.com/289

전력 반도체 기업 동향: 네패스/네패스 아크

애플이 애플카의 자율주행 관련 칩 개발을 국내 반도체 외주조립·테스트기업(OSAT)과 진행하고 있는 것으로 알려졌다. 또 스마트폰의 두뇌인 모바일 애플리케이션 프로세서(AP)의 세계적 강자 퀄

tristanchoi.tistory.com

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체 기술 탐구: 화합물 반도체 개요(feat. SiC, GaN) (2) | 2022.07.17 |

|---|---|

| 반도체 기업 탐구: 장비 기업 현황 update (0) | 2022.07.10 |

| 전력 반도체 기업 동향: 네패스/네패스 아크 (0) | 2022.06.29 |

| 전력 반도체 기업 동향: SK실트론 (0) | 2022.06.29 |

| 전력 반도체 기업 동향: 아이에이 / 트리노테크놀로지 / 파워트론 (0) | 2022.06.28 |

댓글