1. 개요

반도체 후공정에서 이뤄지는 테스트(Test)란, 전기적 특성(Electrical Characteristics) 검사를 통해 칩(Chip)의 불량이 다음 공정으로 넘어가지 않도록 방지함으로써 손실을 최소화하는 과정이다. 초창기의 테스트는 양산 제품에 대해 불량(영구적 오류)을 걸러내는 필터링 위주로 진행했다. 하지만 현재는 신뢰성 불량을 사전 차단하고, 수율을 향상시켜 원가 절감에 기여하며, 제품의 연구∙개발에 도움을 주는 등 그 역할이 점차 확대되고 있다.

반도체 테스트의 목적은 불량 칩을 골라내고, 앞서 진행했던 공정들을 점검해 개선하는 것이다. 이 과정에서 다음 공정으로 불량 칩이 넘어가지 못하게 하는 선별률(Screenability)은 항상 중요한 이슈다.

따라서 Wafer Test는 불량 칩이 불필요하게 패키징(Packaging)되는 것을 방지해 원가를 절감하고, 나아가 수익성을 향상시키는 것이 목표가 된다. Package Test의 경우는 불량 제품이 출하되는 것을 막아 고품질의 반도체를 고객에게 납품하기 위함이다.

또한, 양품이 고객에게 전달된 이후에도 칩에 동작 오류(Fault)가 발생할 수 있는데, 유저가 일정 기간 칩을 오류 없이 안전하게 사용할 수 있도록 제조 과정에서 약한 칩을 미리 골라내어(제품의 전체 생존 기간 중 초창기/중기 불량을 선별) 신뢰성(Reliability)을 확보하는 것이 매우 중요하다. 이렇게 진행된 테스트 결과(Performance)는 내부적인 피드백을 통해 공정을 개선하거나, 반도체 기술 및 제품의 연구∙개발에도 적극 활용되고 있다.

이를 위해 웨이퍼와 패키지/모듈을 테스트하여 검사대상의 불량 여부를 확인한다. 테스트는 크게 온도, 속도, 동작(신뢰성) 3개 부문에서 진행된다.

기존 테스트 공정은 필터 링을 통한 불량 제품의 출하방지를 주목적으로 진행됐다. 하지만 원가 절감 및 공정 개선(수율 향상)을 통한 제품 품질 고도화에 기여하면서 테스트 공정의 중요성은 높아지고 있다.

2. 테스트 항목

테스트는 테스트할 대상의 형태에 따라 웨이퍼 테스트, 패키지 테스트로 구별할 수 있지만, 테스트 항목에 대해서는 아래 표와 같이 온도별 테스트, 속도별 테스트, 동작별 테스트 이렇게 3가지 형태로 구별할 수 있다.

온도별 테스트

테스트 대상에 인가되는 온도가 기준이다. 고온 테스트는 제품의 스펙*에 있는 온도 범위에서 최대 온도보다 10% 이상의 온도를 인가한다. 저온 테스트는 최저 온도보다 10% 이하의 온도를, 상온 테스트는 보통 25℃ 온도를 인가한다. 반도체 제품이 실제 사용될 때는 다양한 온도의 환경에서 사용되기 때문에, 다양한 온도에서의 동작 여부와 온도 마진을 검증하기 위함이다. 메모리 반도체의 경우엔 보통 고온 시험은 85~90℃, 저온 시험은 -5~-40℃를 인가한다.

속도별 테스트

코어 테스트와 스피드 테스트로 구별한다. 코어 테스트는 반도체 제품의 코어 동작, 즉 원래 목적하는 동작을 잘 수행하는지를 평가하는 테스트이다. 메모리 반도체 제품의 경우엔 정보를 저장하는 것이 역할이므로 정보를 저장하는 셀 영역에서 저장이 잘 되는지를 평가, 검증할 수 있는 여러 항목을 테스트한다. 스피드 테스트는 동작 속도를 평가하는 것으로 원하는 속도로 제품이 동작할 수 있는지를 평가한다. 반도체 제품에서 고속 동작이 많아지면서 이 테스트의 중요성이 커지고 있다.

동작별 테스트

DC 테스트, AC 테스트, 기능 테스트 총 3개로 구별할 수 있다. DC 테스트는 전류를 DC로 인가하여 테스트의 결과가 전류 또는 전압으로 나타날 수 있는 항목을 평가하는 테스트 항목이다. AC 테스트는 전류를 AC로 인가하여 AC 동작 특성, 예를 들어 제품의 입출력 스위칭 시간 등의 동적 특성을 평가한다. 기능 테스트는 제품의 각 기능을 동작시켜 정상 동작 여부를 확인하는 테스트이다. 예를 들어 메모리 반도체 제품의 경우에는 메모리 셀(Memory cell)의 정상 동작 여부와 메모리 주변 회로의 정상 동작 여부를 확인한다.

3. 테스트 공정의 종류

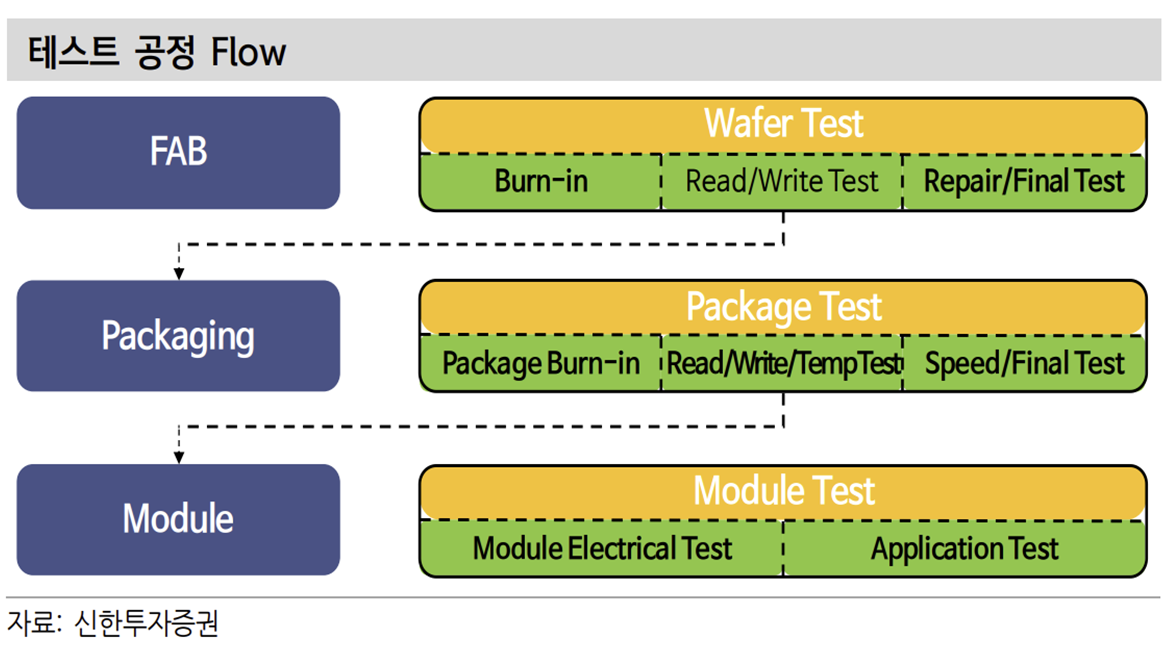

테스트 공정은 검사 대상에 따라 3개(Wafer, Package, Module)로 구분된다.

1) 웨이퍼 테스트(Wafer Test): 전공정에서 제작된 웨이퍼를 받아 전기적인 특성을 테스트한다. 웨이퍼단에서 불량 제품을 사전에 선별할 수 있어 불량 제품에 대한 다음 공정 진행을 방지할 수 있다. 이는 결국 불필요한 공정을 수행하지 않아 수익성 향상으로 연결된다.

2) 패키지 테스트(Package Test): 양품의 웨이퍼를 통해 제작된 패키지가 정상적으로 작동하는지 확인하기 위한 테스트다. 대량의 반도체 다이를 동시에 검사하는 웨이퍼 테스트와 다르게, 패키지 테스트는 각각의 패키지를 정밀하게 테스트 한다. 실제 사용자 환경에서 정상적으로 작동하는지를 확인하고 외관 검사까지 거치게 된다. 테스트는 패키지가 들어있는 패키지 테스트 소켓을 패키지 테스트 보드에 장착하여 진행된다.

3) 모듈 테스트(Module Test): 패키지가 아닌 모듈로 최종 제품이 출하되는 경우 모듈 테스트 공정을 한 번 더 진행하게 된다. 패키지가 실장된 PCB(모듈)에 전기적인 특성을 테스트한 후, 제품이 사용되는 환경에서 여러 동작들이 정상적으로 작동하는지 테스트한다.

3.1.웨이퍼 테스트

웨이퍼 테스트는 테스트 대상이 웨이퍼다. 웨이퍼에는 수많은 칩들이 만들어져 있는데, 이 칩들의 특성과 품질을 웨이퍼 테스트를 통해서 확인하고 검증해야 한다. 이를 위해서는 테스트 장비와 칩을 연결해 칩에 전류와 신호를 인가해야 한다.

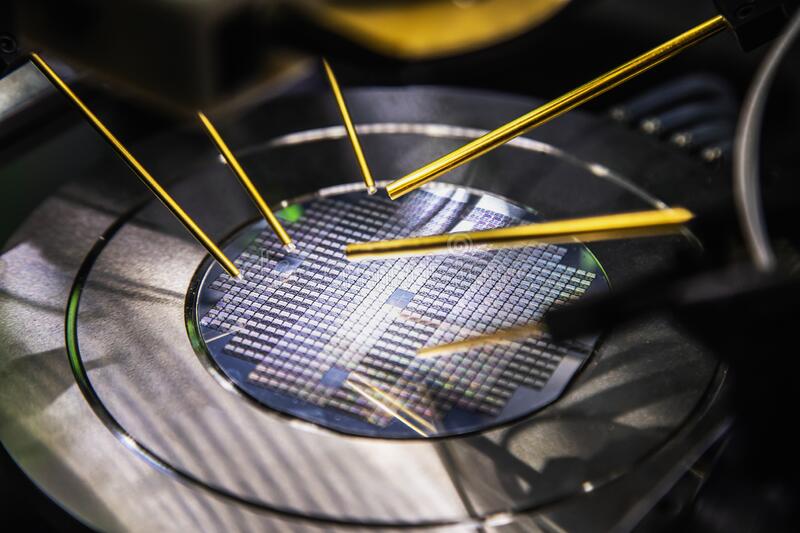

패키지가 완료된 제품들은 시스템에 연결하기 위해 솔더 볼 같은 핀(pin)들이 만들어져 있으므로 테스트 장비와 전기적 연결이 비교적 용이하다. 하지만 웨이퍼 형태의 경우에는 특별한 방법이 필요하다. 이 때문에 필요한 것이 프루브(Probe) 카드이다.

프루브 카드는 아래 그림에서 볼 수 있듯이 웨이퍼의 패드와 물리적으로 접촉할 수 있도록 수많은 탐침

(프루브 카드에서 웨이퍼의 패드와 전기적, 물리적 접촉을 하는 바늘 모양의 침) 카드 위에 형성되어 있다. 그리고 탐침과 테스트 장비를 연결할 수 있는 배선이 카드 내에 만들어져 있다. 이 프루브 카드는 웨이퍼가 로딩되는 웨이퍼 이송 설비에서 웨이퍼와 접촉할 수 있도록 테스터 헤드 부분에 장착된다.

웨이퍼의 전면이 위를 보게 로딩되면 오른쪽의 프루브 카드가 뒤집어진다. 그리고 탐침이 아래를 향하게 테스터 헤드에 장착되고 웨이퍼와 프루브 카드가 접촉할 수 있게 된다. 이때 온도조절 장치는 테스트 온도 조건에 따라 온도를 인가할 수 있다. 테스트 시스템은 실제 프루브 카드를 통해서 전류와 신호를 인가하고 읽어서 테스트 결과를 얻을 수 있다.

프루브 카드는 테스트하고자 하는 칩의 패드 배열, 그리고 웨이퍼에서의 칩의 배열에 따라 그에 맞는 프루브 카드를 따로 제작해서 사용한다. 프루브 카드에서 탐침의 배열은 테스트하고자 하는 칩의 패드 배열과 같다. 그리고 칩의 배열에 따라 탐침의 배열은 반복된다. 그러나 한 번 접촉만으로는 웨이퍼의 모든 칩을 테스트하지는 못한다. 실제 양산에서는 2~3번의 접촉이 진행된다.

웨이퍼 테스트는 보통 ‘EPM(Electrical Parameter Monitoring) → 웨이퍼 번인(Wafer Burn in) → 테스트 → 리페어(Repair) → 테스트’ 순으로 진행한다.

3.1.1. EPM(Electrical Parameter Monitoring)

테스트의 목적은 불량 제품을 걸러내는 것도 있지만, 개발이나 양산 중인 제품의 결함을 피드백하여 개선하는 것도 있다. EPM은 불량을 걸러내는 것보다는 제품의 단위 소자의 전기적 특성을 평가·분석하여 웨이퍼 제작 공정에 피드백하는 것이 주목적이다.

만들어진 웨이퍼가 본격적인 테스트를 하기 전에 설계부서-소자부서가 제시한 제품의 기본적인 특성을 만족하는지를 검사하는 과정으로 트랜지스터 특성, 접촉 저항 등을 전기적 방법으로 측정하는 공정이다. 테스트 관점으로는 소자의 전기적 특성을 활용하여 DC 인자(Parameter)를 추출하고 각 단위 소자의 특성을 모니터링할 수 있다.

3.1.2. 웨이퍼 번인(Wafer Burn in)

3.1.3. TDBI(Test During Burn In)

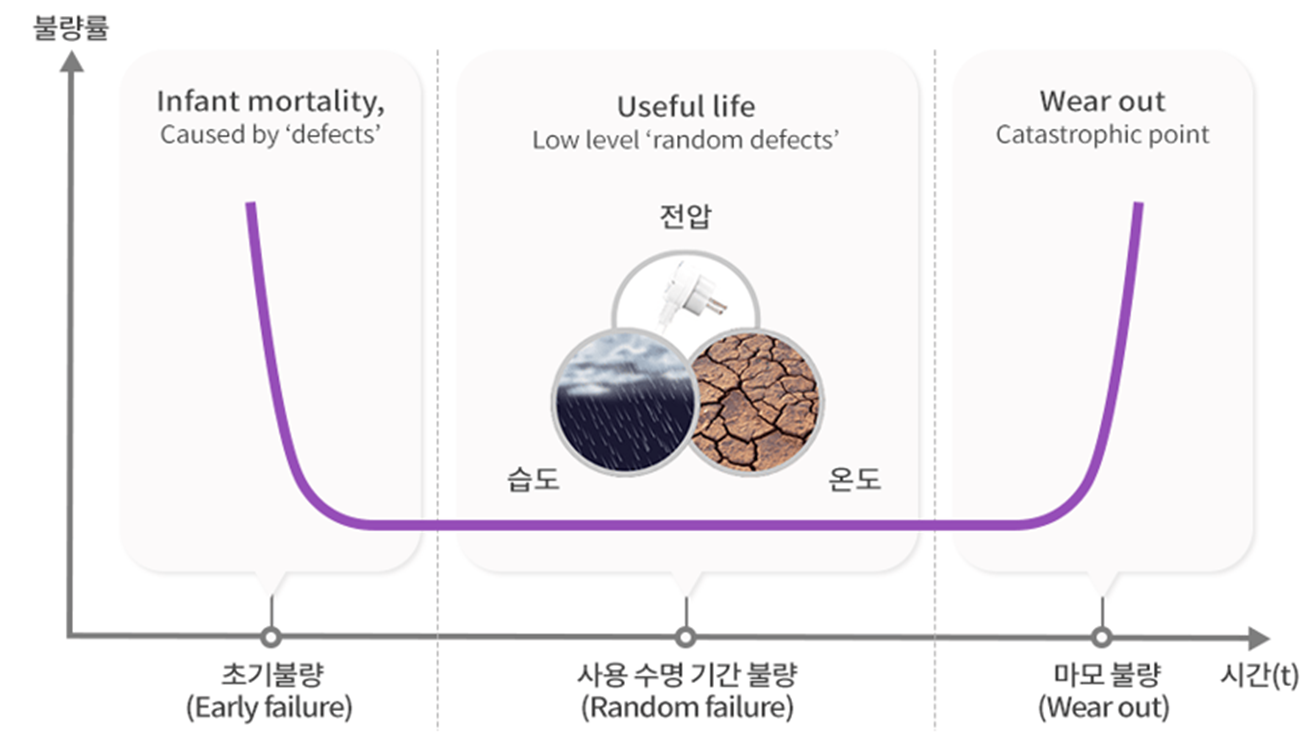

위 그림은 제품 수명 동안의 불량률을 시간 함수로 표현한 것이다. 모양이 욕조 모양을 닮았다고 해서 욕조(Bath tub) 그래프라고도 불린다. 수명 초기에는 제품 제조상 불량 때문에 생기는 고장, 즉 초기 불량(Early failure)이 많다. 제조상에서 오는 불량이 사라지면 그 제품의 사용 수명 동안은 불량률이 낮아진다(Random failure). 그리고 그 제품이 수명이 다하면(Wear out) 다시 불량률이 높아진다. 만들어진 제품을 바로 고객에게 준다면 초기 불량 때문에 고객 불만이 높아지고, 반품 등의 이슈가 생길 가능성도 높다.

제품이 가지고 있는 잠재적인 불량을 유도하여 초기 불량을 미리 선별하기 위해 하는 것이 번인(Burn in)이다. 웨이퍼 번인은 온도와 전압을 인가하여 웨이퍼 상태의 제품에 스트레스를 줌으로써 초기 불량 기간에 나타날 수 있는 불량이 모두 드러나게 만드는 것이다.

3.1.4. 테스트

웨이퍼 번인(Wafer Burn in)으로 초기 불량을 도출한 웨이퍼는 프루브 카드로 웨이퍼 테스트를 실시한다. 웨이퍼 테스트는 웨이퍼 레벨에서 칩의 전기적 특성을 검사하는 공정이다. 불량 칩 사전 검출, 패키지/실장에서 생길 불량을 미리 선별해 웨이퍼 레벨 불량 원인 분석 및 제조 공정 피드백, 웨이퍼 레벨 분석(Wafer Level Verification)을 통한 소자 및 설계 피드백 등이 주요 목적이다.

웨이퍼 테스트에서 불량을 선별하게 되면 불량인 셀의 일부는 다음에 설명할 리페어(Repair)라는 과정을 통해 여분의 셀(Redundancy cell)로 대체할 수 있다. 리페어 공정 후에는 이렇게 대체된 셀이 제대로 역할을 하여 칩이 스펙을 만족하는 양품으로 판정할 수 있는지를 확인하기 위해 다시 한번 웨이퍼 테스트를 진행하게 된다.

3.1.5. 리페어(Repair)

리페어는 주로 메모리 반도체에서 수행하는 공정으로 불량 셀을 여분의 셀로 대체하는 리페어 알고리즘(Repair Algorithm)이 적용된다. 예를 들어, DRAM 256bit 메모리의 웨이퍼 테스트 결과 1bit가 불량이면 이 제품은 255bit가 된다. 하지만 여분의 셀이 불량인 셀을 대체하면, 다시 256bit를 만족시키고 고객에게 판매할 수 있는 양품이 된다. 리페어를 통해서 결국 수율이 증가하는 것이다. 이 때문에 메모리 반도체는 설계 시 여분의 셀을 만들어 테스트 결과에 따라 대체할 수 있게 한다.

하지만 불량을 대비한 여분의 셀을 만든다는 것은 그만큼 공간을 차지하고, 칩 크기를 키우는 것이다. 그 때문에 모든 불량을 대체할 수 있는 여분의 셀, 예를 들어 256bit 모두를 대체할 수 있는 여분의 256bit를 만드는 것은 불가능하다. 그래서 공정 능력을 고려하여 수율 증가 효과를 최대로 나타낼 수 있는 수준의 여분의 셀을 만든다. 즉, 공정 능력이 좋아서 불량이 적다면 여분의 셀을 적게 만들어도 되고, 공정 능력이 좋지 않아서 불량이 많을 것으로 예상된다면 여분의 셀을 더 만들게 되는 것이다.

리페어는 열(Column) 단위 리페어와 줄(Row) 단위 리페어로 나뉜다. 열에 여분의 열을 만들어 불량 셀이 있는 열을 여분의 열로 대체하는 것이 열 단위 리페어이고, 여분의 줄을 만들어 불량 셀이 있는 줄을 여분의 줄로 대체하는 것이 줄 단위 리페어다.

DRAM의 리페어 공정은 불량 셀이 있는 열이나 줄의 물리적 연결을 끊어 단선이 되게 하고, 여분의 셀이 있는 열이나 줄을 연결한다. 리페어는 레이저 리페어와 e-퓨즈 리페어가 있다. 레이저 리페어는 레이저로 배선을 태워서 불량 셀의 연결을 끊는다. 이를 위해선 외부에서 배선에 레이저를 쏠 수 있도록 배선이 노출되어야 한다.

그래서 웨이퍼의 패드 주변에 열이나 줄과 연결된 배선이 노출되도록 칩의 보호층(Passivation layer)이 벗겨진(Open) 영역을 만들어 놓고, 레이저 리페어를 한다. 레이저 리페어는 웨이퍼 테스트 공정에서만 가능하다. 왜냐하면 패키지 공정을 진행하고 나면 칩의 표면이 패키지 재료에 의해서 다 덮히기 때문이다.

e-퓨즈 리페어는 배선에 높은 전압이나 전류를 인가하여 불량 셀의 연결을 끊는 것이다. 이 방법은 내부 회로에서 리페어되기 때문에 배선 노출을 위해 칩의 보호층을 벗긴 영역을 만들 필요가 없고, 테스트 공정에서뿐만 아니라 패키지 테스트 공정에서도 작업 가능하다.

3.2. 패키지 테스트

웨이퍼 테스트에서 양품으로 판정된 칩은 패키지 공정을 진행하고, 완성된 패키지는 다시 한번 패키지 테스트를 진행한다. 웨이퍼 테스트 시 양품이었던 것도 패키지 공정 중 불량이 발생할 수 있으므로 패키지 테스트는 꼭 필요하다. 웨이퍼 테스트는 동시에 여러 칩을 테스트하는 장비 성능의 한계로 원하는 항목을 충분히 테스트하지 못할 수도 있다. 반면에 패키지 테스트는 패키지 단위로 테스트하기 때문에 장비에 주는 부담이 적다. 따라서 원하는 테스트를 충분히 진행하여 제대로 된 양품을 선별할 수 있다.

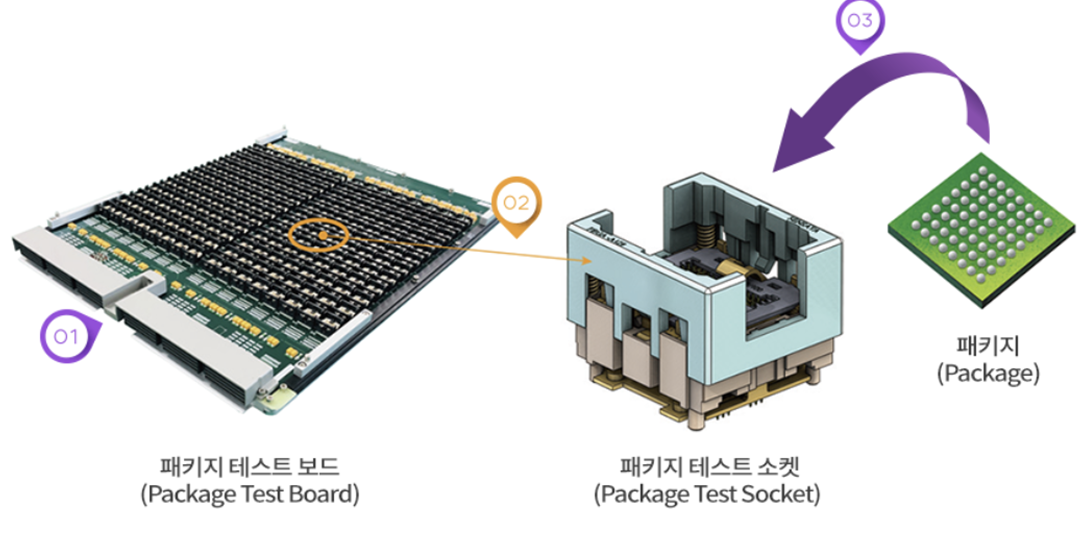

패키지 테스트를 위해서 먼저 위 그림의 3번처럼 패키지의 핀(pin, 그림에서는 솔더 볼)이 아래쪽을 향하도록 패키지 테스트 소켓에 넣어 소켓에 있는 핀들과 물리적으로 접촉하게 한다. 그리고 이 패키지 테스트 소켓을 패키지 테스트 보드(Package Test Board)에 장착하여 패키지 테스트를 진행한다.

3.2.1. TDBI(Test During Burn In)

제품의 잠재 불량을 초기에 제거하기 위해 제품에 전압과 온도로 스트레스를 가하는 테스트가 번인(Burn in)인데, 패키지로 만든 후 실시하는 번인은 TDBI라고 부른다. 번인은 웨이퍼에서 할 수도 있고, 패키지에서 할 수도 있지만 대부분의 반도체 제품은 웨이퍼와 패키지에서 번인을 동시에 적용한다. 제품의 특성을 잘 파악했다면 번인 시간과 공정 수를 줄이는 조건을 찾아서 번인을 실시하는 것이 양산의 개념에서는 가장 효율적이다.

3.2.2. 테스트

데이터시트에 정의된 동작이 사용자 환경에서 정상적으로 동작하는지 판단하는 공정이다. 온도 코너 테스트를 실시하여, 제품에 AC/DC 인자 약점 및 Cell & Peri 영역에서 고객이 요구하는 동작이 스펙을 만족하는지 검증한다. 이때 데이터시트 조건보다 좀 더 열악한 조건 및 최악의 동작 조건을 조합하여 테스트를 실시한다.

3.2.3. 외관(Visual) 검사

테스트가 완료되면 테스트 결과, 특히 스피드 구분이 필요한 경우 스피드 특성을 패키지 외관에 기록해야 하는데 이 때문에 레이저 마킹(Marking)이 필요하다. 패키지 테스트가 완료 후 마킹까지 진행했다면, 패키지 트레이(tray)에 테스트 결과 양품인 패키지를 담으면 남은 단계는 고객 출하뿐이다. 그러므로 고객 출하 전에 최종적인 외관 검사를 실시하여 외관 불량도 선별해야 한다. 외관 검사 시 보디에서는 균열 / 마킹 오류 / 트레이에 잘못 담은 것 등을 선별하고, 솔더 볼에서는 볼 눌림, 볼이 없는 것 등을 선별한다.

출처: SK하이닉스, 신한투자증권, 한올미디어

뜨리스땅

https://tristanchoi.tistory.com/279

반도체 기술 탐구: 반도체 패키지 시장 흐름 3 - FC BGA 대면적화

FC-BGA 대면적화 FC-BGA는 전통적으로 CPU, GPU, FPGA(Field Programmable Gate Array), ASIC 등 고성능 프로 세서를 위해 쓰인다. 이들 프로세서는 주로 DRAM, 칩셋 등과 함께 패키지된다. 또한 최근에는 모듈형 디

tristanchoi.tistory.com

'반도체, 소.부.장.' 카테고리의 다른 글

| 반도체 산업 탐구: DDR5 효과 지속, 우려대비 견조할 ASP (1) | 2023.05.22 |

|---|---|

| 반도체 기술 탐구: 반도체 패키지 공정 개요 (2) | 2023.05.06 |

| 반도체 기업 리뷰: 23Q1, 주성엔지니어링 (0) | 2023.05.03 |

| 반도체 산업 탐구: 예상대로 부진한 장비사 실적. 그러나.. (0) | 2023.05.02 |

| 반도체 산업 탐구: OSAT 투자 전략 (0) | 2023.04.24 |

댓글