1. TSV 중심 전반 요약

2. 세부 공정 별 순서

1) Silicon Etch: 실리콘을 식각하여 깊은 트렌치(trench, 구멍)를 형성하는 공정

FEOL 공정 이후 웨이퍼를 식각하여 트렌치를 만드는 공정이다. 식각 공정에 사 용되는 PR(감광액, Photoresist)만으로 하부층을 식각하기 어렵다. 트렌치의 깊이 가 깊기 때문에 높은 선택비가 생산성 향상에 기여하기 때문이다. 이에 TSV는 트렌치를 형성할 때 HM(하드마스크, Hardmask)을 활용하여 식각을 진행한다.

2) TSV Cu Fill: 트렌치에 전도성 재료인 구리(Cu)를 채우는 공정

트렌치에 전도성이 있는 Cu(구리)를 채우는 공정이다. Cu는 실리콘(웨이퍼)에 치 명적인 오염을 야기할 수 있는 물질이다. 이를 방지하기 위해 Cu를 채우기에 앞 서 실리콘과 Cu 사이에 절연층(Oxide, Nitride 등) 및 박막층(Seed, Barrier)을 증 착한다. 박막 형성된 트렌치에 TSV Cu Fill(Cu 충전 공정)을 진행한다. 트렌치의 깊이가 깊기 때문에 Via(비아) 내부에 보이드 없이 채우는게 핵심이다.

3) TSV Cu CMP: 웨이퍼 윗면에 있는 Cu를 제거하는 공정

웨이퍼 윗면을 평탄화하고 불필요한 물질을 제거하는 공정이다. TSV Cu Fill 공정 으로 절연층∙박막층과 Cu가 웨이퍼 윗면에 위치한다. 이 증착된 물질을 제거하여 트렌치에만 Cu가 채워지도록 하는 공정이다.

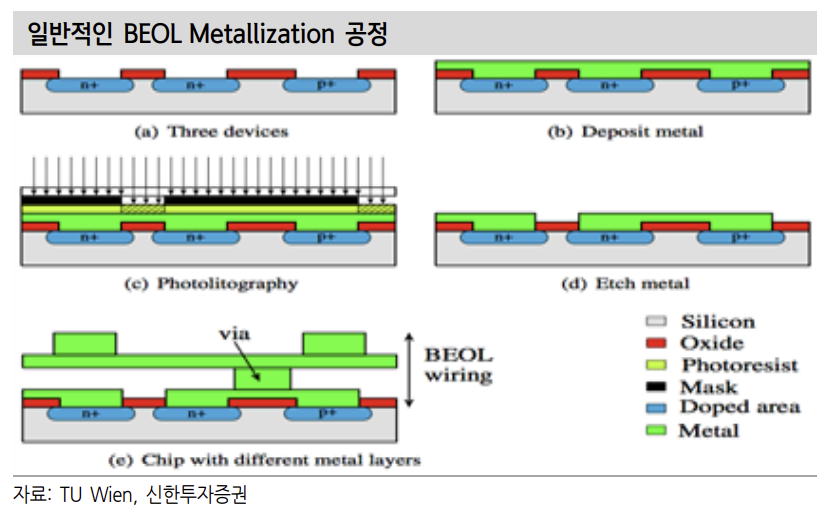

4) BEOL Metallization: 외부와의 전기적인 연결을 위해 회로 패턴에 따라 금속선을 이어주고 알루미늄 패드를 형성하는 공정

BEOL(후속 배선 공정)은 외부와의 전기적인 연결을 위해 포토, 식각, 증착 등의 공정을 통해 소자와 전원, 소자와 소자를 연결해주는 공정이다. 외부 전원을 받 지 못하고 서로 연결되지 않는 소자는 아무런 역할을 할 수 없기 때문이다.

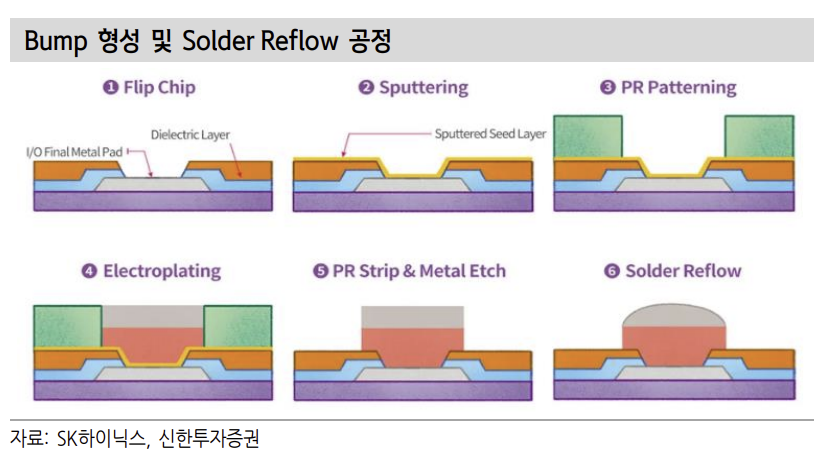

5) Front Side Bump Formation: 웨이퍼 앞면에 범프를 형성하는 공정

HBM은 여러 개의 메모리 칩을 수직으로 적층한 칩 적층 패키지 형태다. 수직 적층된 칩을 전기적으로 연결하기 위해 칩의 한 면이 아닌 양면에 범프를 형성 키여야한다. 이후 리플로우 공정을 할 때 범프가 볼 형태를 유지하는데 도움을 주는 절연층을 형성한 이후 기둥을 세우고 범프를 형성하는 공정을 진행한다.

6) Wafer Solder Reflow: 열을 이용하여 솔더 범프 구형으로 만드는 공정

리플로우 공정을 통해 범프를 볼 형태로 만들어 준다. 1) 범프 간 높이 차이를 최 소화, 2) 범프 표면의 거친 정도를 최소화, 3) 산화물 제거가 진행된 볼 형태의 범 프는 적층 과정에서 접합성을 높이는데 유리하다.

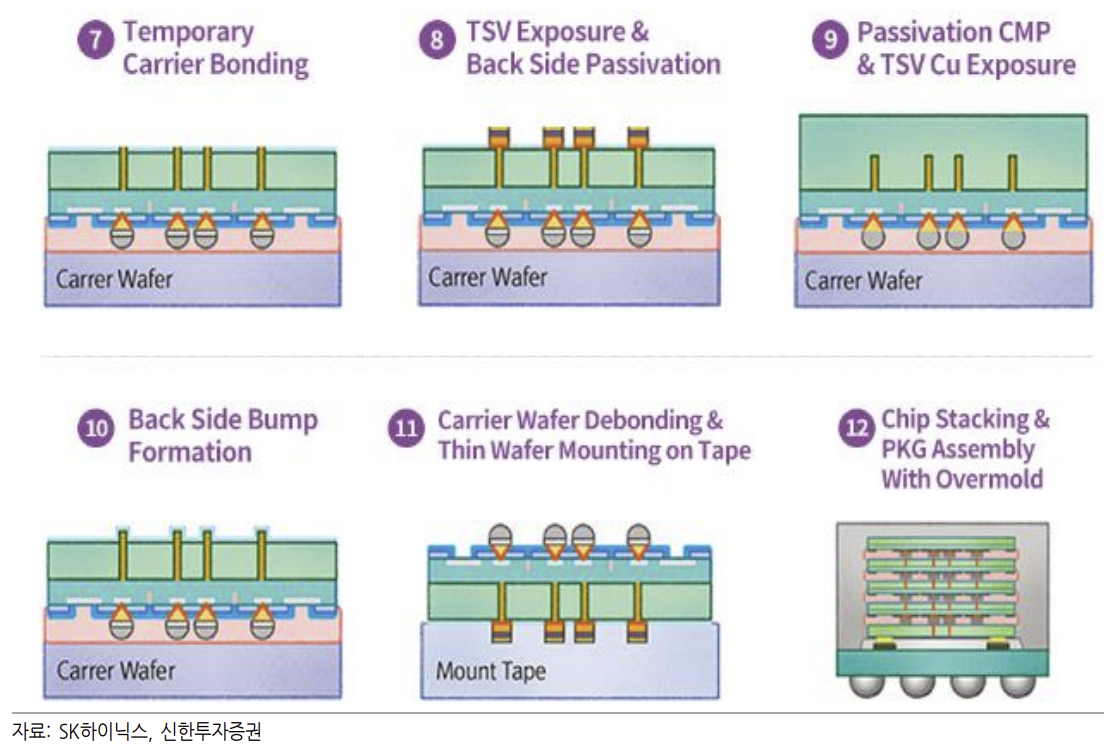

7) Temporary Carrier Bonding: TSV 패키지를 위해서 웨이퍼에 캐리어를 붙여주는 공정

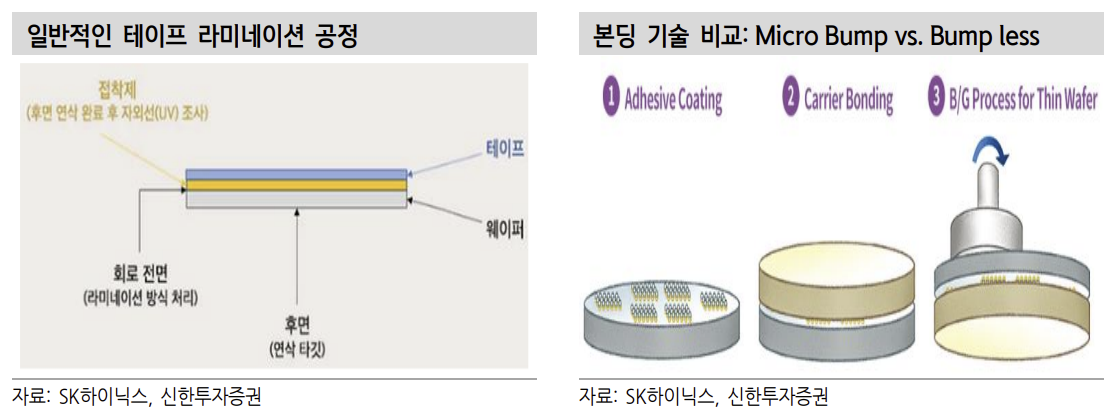

전공정을 거친 웨이퍼는 후면을 얇게 갈아내는 백그라인딩 공정이 요구된다. 그 이유는 1) 전공정을 거치며 생긴 오염된 부분을 제거하고, 2) 웨이퍼의 두께를 줄 이고, 3) 전력 소모를 낮추고, 4) 열을 후면으로 빠르게 내보낼 수 있기 때문이다. 백그라인딩 공정을 진행할 때 웨이퍼를 얇게 갈아내는 힘에 의해 웨이퍼가 깨지 는 현상이 발생한다. 이를 방지하기 위해 일반적인 후공정에서는 웨이퍼 앞면에 테이프를 붙여 웨이퍼를 보호한다. 하지만 웨이퍼 뒷면에 범프를 형성해야하는 TSV 공정에서는 테이프가 아닌 캐리어 웨이퍼를 부착하여 웨이퍼를 보호해준다.

8) TSV Expousre & Bake Side Passivation: 외부와 차단된 TSV를 노출시키고 절연층을 형성시키는 공정

백그라인딩이 진행된 웨이퍼 후면의 두께는 얇아졌지만 여전히 TSV는 웨이퍼 내부에 숨겨져있다. 전기적 연결 통로인 TSV를 통해서 칩들을 연결해야하기 때 문에 식각 공정을 통해 숨겨져있는 TSV를 노출시켜주는 공정이 요구된다. 이후 노출된 TSV를 보호하기 위해 보호막을 코팅하는 Passivation 공정을 진행한다.

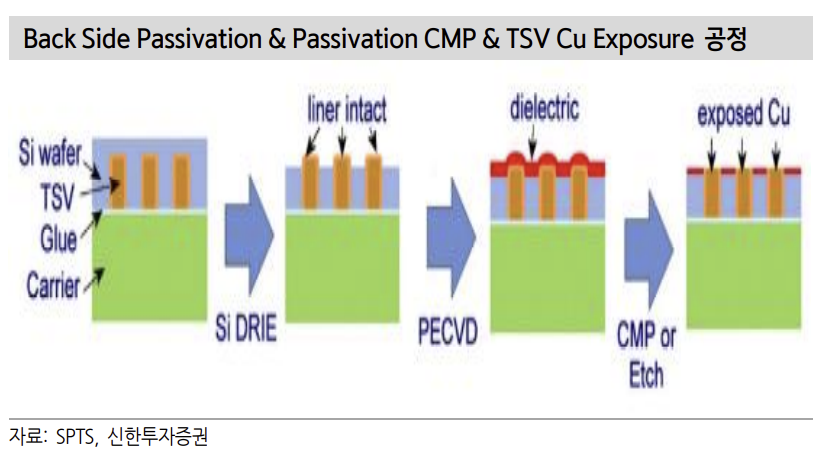

9) Passivation CMP & TSV Cu Exposure: 절연층을 평탄화하고 외부와 차단된 TSV Cu Via를 노출시키는 공정

TSV를 보호하기 위한 절연층이 증착된 상태로 TSV는 절연층 내부에 숨겨져 있 다. 절연층을 평탄화하여 절연층이 코팅된 TSV를 노출시키는 공정이다.

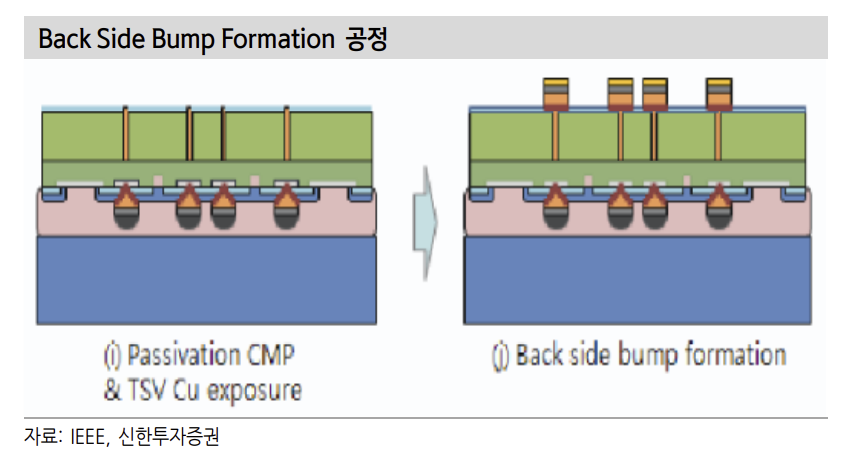

10) Back Side Bump Formation: 웨이퍼의 후면에 범프를 형성하는 공정

기존에는 앞면에만 범프를 형성했다. 하지만 칩을 수직 적층하기 위해서는 전기 적 연결 통로인 범프를 양면에 형성해야한다. 앞선 공정에서 칩 앞면에 범프를 형성했기 때문에 이번 공정에서는 칩의 후면에 범프를 형성해준다.

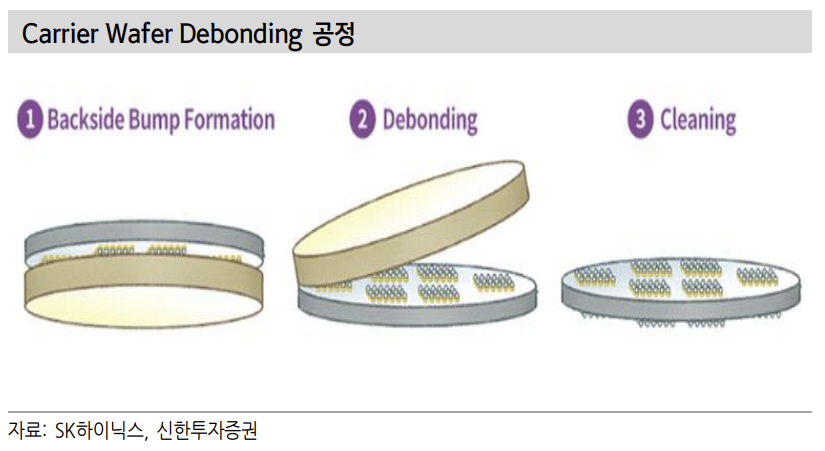

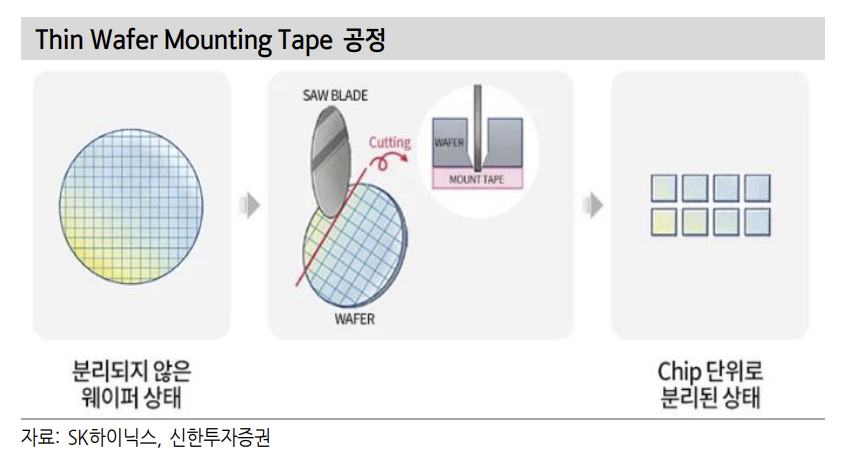

11) Carrier Wafer Debonding & Thin Wafer Mounting Type: 웨이퍼 뒷면에 붙였던 캐리어를 제거하고 뒷면을 그라인딩하여 얇게 만든 웨이퍼를 Mount Tape에 고정시키는 공정

백그라인딩 공정(웨이퍼 후면을 얇게 갈아내는 공정)에서 웨이퍼를 보호하기 위 해 부착했던 캐리어 웨이퍼를 제거한다. 캐리어 웨이퍼를 부착할 때 사용했던 가 접착용 접착제의 잔여물이 남아있지 않도록 세정 공정을 진행한다. 이후 다이싱 공정을 위해 그라인딩된 얇은 웨이퍼 뒷면에 마운팅 테이프를 붙여준다. 웨이퍼 를 개별 칩 단위로 절단할 때 웨이퍼가 휘는 현상을 방지하기 위해서다.

12) Chip Stacking & PKG Assembly with Overmold: TSV 형성된 칩 앞면과 뒷면에 각각 형성된 범프들을 본딩하여 적층시키는 공정

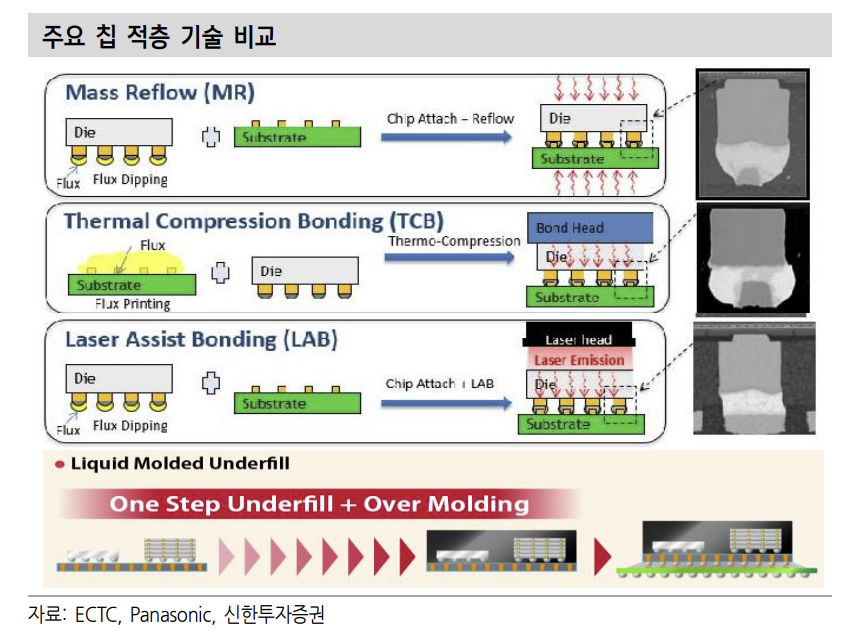

앞선 공정에서 만들어진 칩을 칩 또는 인터포져/기판에 적층하는 공정이다. 적층 된 제품들끼리 전기적 연결을 위해 본딩이라는 공정을 진행한다. 현재 적층 과정 에서 활용되고 있는 본딩 기술은 크게 4가지로 요약할 수 있다

- MR(Mass Reflow)

MR 본딩은 대량의 범프에 열을 가하여 칩과 칩 또는 칩과 기판/인터포져를 본 딩하는 기술이다. 범프가 부착된 칩을 리플로우 장비에 통과시키면서 칩 전체에 열을 가하여 접합하는 방식이다. 과거에는 많이 활용된 기술이었다. 하지만 범프 의 크기가 작아지면서 범프 간 거리가 좁아졌다. 이에 범프들 간의 브릿지가 발 생하는 문제가 발생하기 시작했다. 칩의 두께 또한 얇아지면서 고열에 의해 칩이 휘거나 부서지는 현상이 나타나기도 했다.

- TCB(Thermal Compression Bonding)

MR 본딩의 기술 한계를 극복하기 위해 사용된 기술로 TC 본딩은 열과 압력을 가하여 본딩하는 기술이다. 적층하려는 칩과 칩 또는 칩과 기판/인터포져 사이에 절연 물질(페이스트, 필름)을 집어 넣는다. 절연 물질에 열과 압력을 가하여 최소 한의 어긋남으로 범프간 연결을 진행한다. HBM 생산 공정에서는 최소 1,024개 의 범프가 요구되기 때문에 정밀한 작업이 요구가 된다.

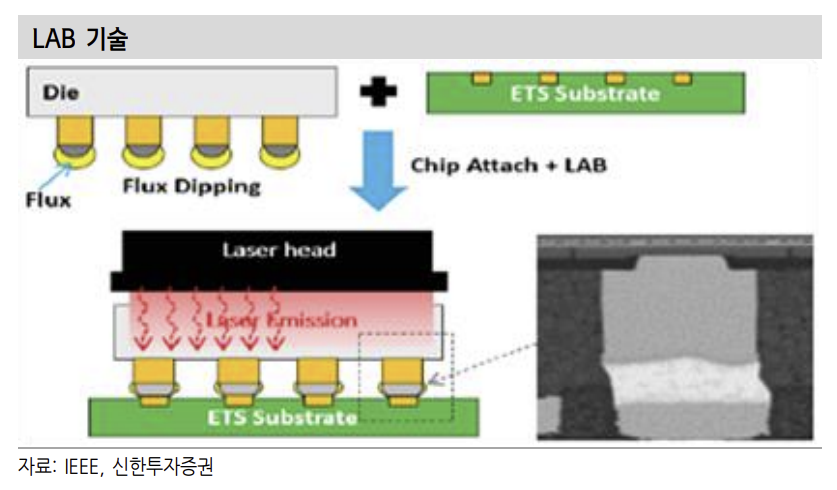

- LAB(Laser Assist Bonding)

차세대 본딩 기술로 칩과 칩 또는 칩과 기판/인터포져 접합부에만 레이저 빔을 가하여 본딩하는 기술이다. 칩 전반에 고열을 가하는 MR 및 TC 본딩과 다르게 접합부에만 레이저 빔을 가하기 때문에 Thermal Stress가 낮다. 또한 공정 소요 시간은 한 영역당 1~2초 정도로 짧아 생산성 향상에 크게 기여할 수 있다.

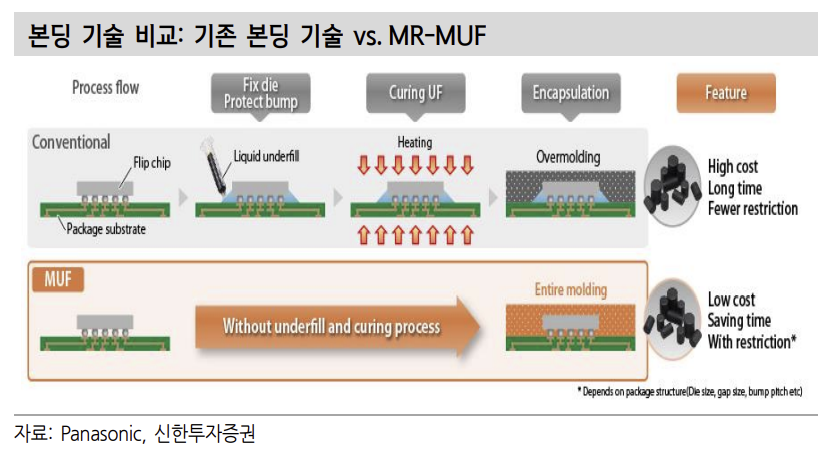

- MR-MUF(Mass Reflow Molded Underfill)

MR 본딩을 진행한 이후 MUF(Molded Underfill) 공정을 통해 칩 사이의 공백 을 채워주는 동시에 몰딩 공정까지 한번에 진행하는 기술이다. MR 공정에서 활 용되는 소재를 개선하여 칩에 가열하는 온도를 낮췄다. 고열에서 진행되는 MR 공정의 문제점(브릿지, 칩이 휘어지는 현상 등)을 일부 보완한 방법이다. 기존 기 술(MR Bonding) 대비 40% 얇은 칩에 열을 가해도 생산이 가능하다.

공정 속도가 상대적으로 빠른 장점을 갖고 있다. 칩들 사이의 공백을 채워주는 언더필 공정과 몰딩 공정(물리적/화학적 충격에 보호하기 위해 칩을 EMC로 감 싸주는 공정)을 동시에 진행하기 때문에 공정 속도가 단축될 수 있다.

출처: 신한투자증권, Panasonic, SK Hynix, IEEE, ECTC, SPTS

뜨리스땅

https://tristanchoi.tistory.com/510

HBM 반도체 Value Chain 및 관련 업체 리스트

- 전공정 장비 및 부품: 오픈엣지테크놀로지, 에스티아이, 오로스테크놀로지, 제우스, 케이씨텍, 파크시스템스, 넥스틴, 테스, 미코 - 후공정 장비 및 부품: 피에스케이홀딩스, 한미반도체, 프로

tristanchoi.tistory.com

https://tristanchoi.tistory.com/458

반도체 기술 탐구: SK Hynix의 HBM 패키징 기술, TSV와 MR-MUF

1. TSV HBM 기사가 나오면 단골손님처럼 등장하는 기술 용어가 'TSV'이다. TSV는 'Through Silicon Via'의 줄임말로 실리콘(반도체 wafer)를 관통하는 만드는 배선, 즉 '실리콘관통전극'이다. 반도체의 집적도

tristanchoi.tistory.com

https://tristanchoi.tistory.com/277

반도체 기술 탐구: 차세대 패키지 기술 종합 2(인터포저란 무엇인가?)

1. 인터포저의 정의 인터포저(Interposer)는 복수 칩 결합을 위해 사용되는 패키지 기술 중 하나로, 피치(Pitch) 차이가 큰 반도체 칩(Semiconductor Chip)과 기판(Substrate)를 전기적으로 연결하기 위해 삽입

tristanchoi.tistory.com

https://tristanchoi.tistory.com/477

반도체 기술 탐구: CoWoS와 InFO

1. CoWoS란 무엇인가? CoWoS는 2.5D 패키지 기술을 의미하는 TSMC의 브랜드명으로, 2개 이상의 반도체 칩을 웨이퍼 상에서 상호 연결한 뒤 패키지 기판에 올린다는 뜻이다. 따라서 CoWoS 역시 기존 2.5D 패

tristanchoi.tistory.com

https://tristanchoi.tistory.com/515

삼성전자와 SK하이닉스의 HBM 접근 방법

1. SK하이닉스의 HBM은 MR-MUF로 HBM은 2013년 12월 SK하이닉스가 세계 최초로 개발한 이후 HBM2→HBM2e→HBM3→HBM3e로 개발되어 왔다. HBM을 적층하는데 있어 SK하이닉스는 HBM2까지는 NCF(Non Conducted Film)를 사

tristanchoi.tistory.com

'반도체, 소.부.장.' 카테고리의 다른 글

| 2023 2H 반도체 장비 업체 시황 점검 - 2/2 (0) | 2023.11.08 |

|---|---|

| 2023 2H 반도체 장비 업체 시황 점검 - 1/2 (0) | 2023.11.07 |

| HBM 반도체 Value Chain 및 관련 업체 리스트 (0) | 2023.11.06 |

| SK하이닉스 - 2023 3Q update (0) | 2023.10.31 |

| 반도체 장비 기업 - HPSP (0) | 2023.10.21 |

댓글